Breadcrumb

Circuit Theory and Applications

Microfactory strategic decision making using simulation

This paper aims to study how the agility concept is successfully applied in manufacturing facilities. The study is involved in selecting the industry and the machines for the novel Microfactory established at Nile Preneurs, Nile University, with focus on the sheet metal workshop located in the Microfactory. The recommendations of this work include the most suitable layout, scheduling technique according to the manufacturing lead time, utilization, work in process, tool change over and distance travelled by operators. Flexsim simulation software is used to determine the optimum combination of

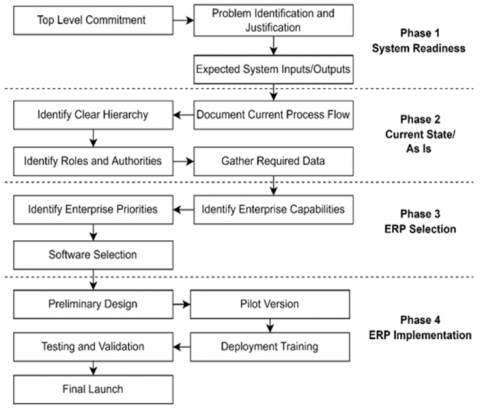

Novel Integrated Framework for ERP Selection and Implementation

As the economic pressure on businesses increases, organizations try to adopt innovative technology solutions to cope with this pressure and adapt to the rapid market changes. Particularly for small and medium enterprises (SMEs). They must integrate all resources and information levels to highly utilize their limited resources and survive the local and global competition. This could be achieved by adopting the best suitable Enterprise Resource Planning (ERP) system. On the other hand, properly selecting and implementing the right ERP system is challenging for many reasons. Hence, this paper

Organic Binding Materials in Cotton Waste

The continued logging for hardwood in subtropical rainforests is causing deforestation and the destruction of diverse environmental ecosystems. Synthetic plastics and particle boards containing synthetic binders such as formaldehydes are alternatives to hardwood, both of which are harmful to the environment and human health. To eliminate wood logging, various biomaterials could be used as promising alternatives to wooden materials. Cotton have been shown to be a viable alternative to various types of wood. Binders are essential in the production of composite wood from cotton. Natural

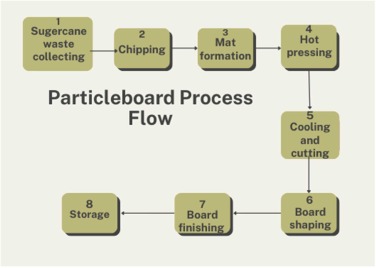

Sustainable utilization of sugarcane bagasse for wood-based panels: A promising approach for waste management in Egypt

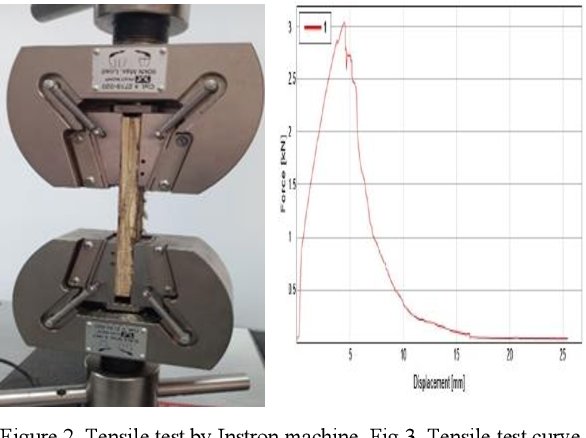

One method to sustainable development is to reduce waste generation and recycle it in a way that contributes to the economic, social, and environmental goals of sustainable development. The study focuses on particle board production from Sugar Cane Bagasse (SCB). Various fiber-matrix combinations were used to create composites using SCB and epoxy resin matrix. Mechanical testing and water absorbance tests were employed to assess the effects of the epoxy content (0–25 wt%). The outcomes demonstrated that the optimal tensile strength of bio composites was attained by the 25 wt% of epoxy with SCB

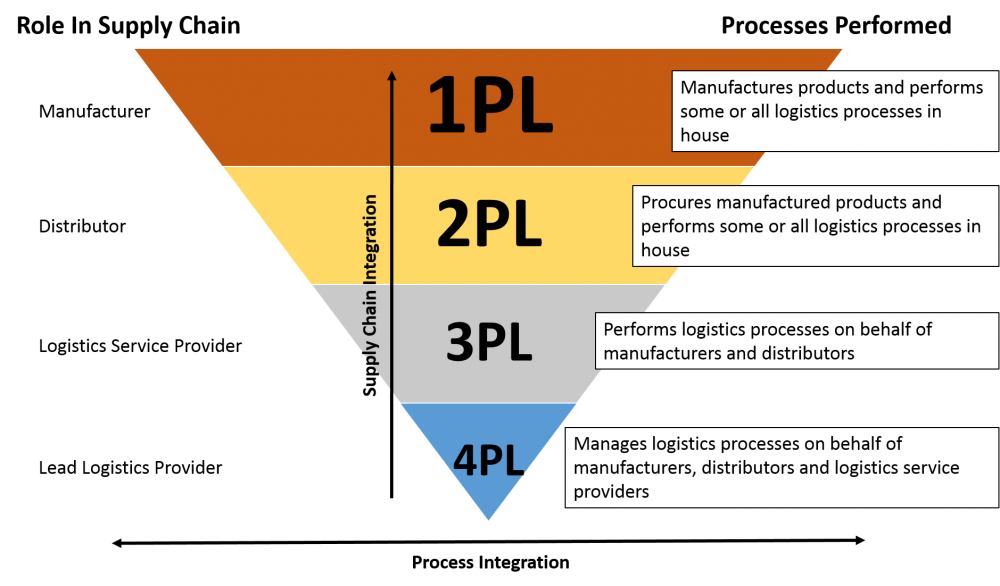

Modelling of 3rd Party Logistics Provider Using Unified Modelling Language

Transportation is a vital driver in logistics management. Third party logistics (3PL) involves a company outsourcing logistics services to other companies. Third party logistics aids in facilitating and optimizing transportation by aggregating demand for trucks and drivers. This paper proposes a model of a transportation 3PL System. The system under study is modelled using the Unified Modelling Language 2.0 (UML 2.0) through an analysis of 3PL provider located in Egypt. The system is analyzed and identified with Integrated Definition for Function Modeling Diagram (IDEF0) & context diagram

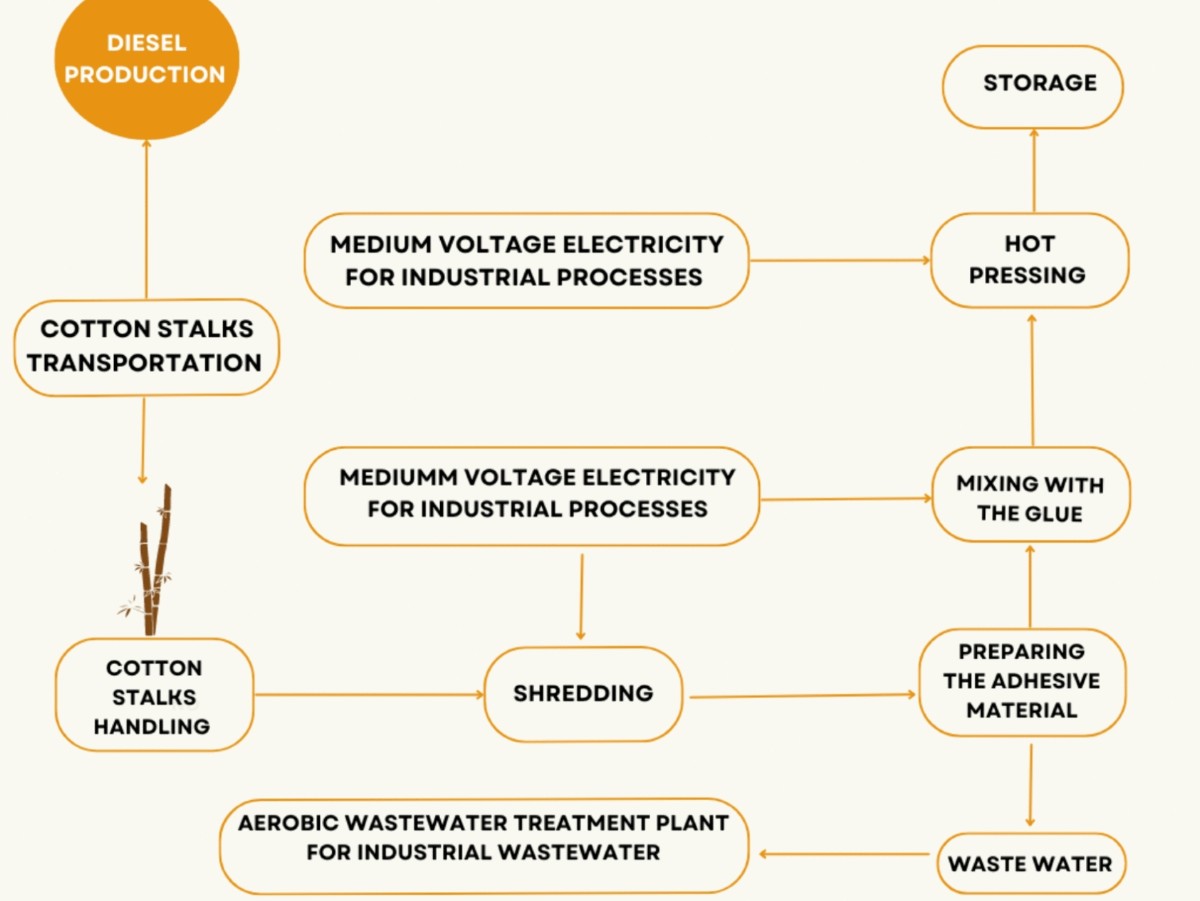

Utilization cotton stalks as a raw material for wooden products

Wood is one of the most used materials in the construction industry. However, the traditional source of wood, which is forestry, has some negative impacts on the environment. Hence, there have been increased efforts to find alternative sources of wood to minimize environmental degradation. Cotton stalks have been identified as a potential raw material for this industry, and research has shown that this material has good potential to replace wood. Furthermore, the disposal of cotton stalks is a significant environmental problem in many regions. This study discusses utilizing cotton stalks for

Fabricating Starch-Based Bioplastic Reinforced with Bagasse for Food Packaging

Nowadays, food packaging plastics is one of the largest markets that consume thermoplastics. Regardless, the packaging industry accounts for the majority of plastic waste that is polluting the environment. Furthermore, because petroleum sources are limited and on the verge of depletion, there is a need to develop alternative materials that can perform the same functions as conventional plastics. Hence, many solutions have emerged in the now time being. Biopolymers have demonstrated great potential as green materials, despite their poor market penetration. They can be a very remarkable

Mechanical and environmental performance assessment of cotton stalk composites with natural adhesives for sustainable construction materials

Carbon dioxide emissions pose a global issue, with deforestation, forest loss from logging, fires, and construction highlighting the adverse effects of climate change. Urgent action is required to reduce carbon dioxide emissions and preserve forests. Egypt can contribute to reducing greenhouse gas emissions by effectively utilizing its waste resources, especially agricultural waste. The research focuses on developing environmentally friendly and sustainable construction materials with a forward-looking approach. This involves exploring alternative options for synthetic formaldehyde adhesives

Investigation of a novel drying technique in tableware production process

The primary by-product of the sugarcane industry is sugarcane bagasse, which is considered a raw material for molded tableware production process. Studies proved that this industry is energy and water intensive. Attempts have been conducted to produce biodegradable bagasse plates utilizing a novel drying technique for the bagasse pulp using mechanical rollers for dehydration and cold drying instead of conventional vacuum drying. It was found that the new drying mechanism reduces the energy consumed by 32% and water consumption by 90% compared to the traditional molded tableware manufacturing

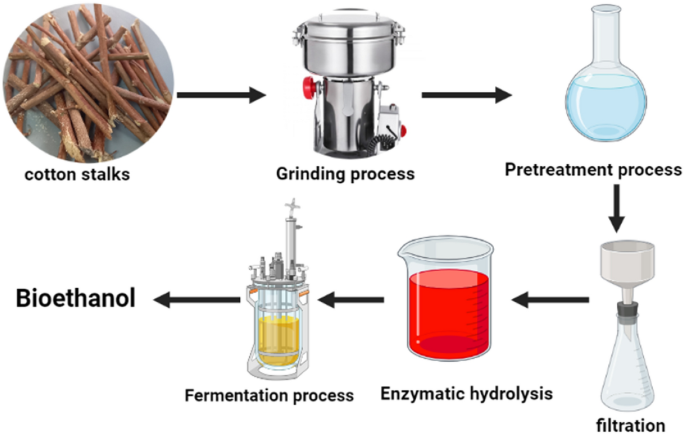

A comparative cradle-to-gate life cycle assessment of three cotton stalk waste sustainable applications

This paper presents a novel approach to utilizing agricultural waste. It compares three different applications for cotton stalks: fabrication of wood composites, bioethanol production, and biogas cradle-to-gate Life cycle assessment production processes. Cotton cultivation generates a lot of debris, mostly cotton stalks, which are incinerated or landfilled, Sustainable resource management is critical for maintaining the ecosystem, and economic stability, and promoting social fairness since it ensures the long-term availability of resources while minimizing environmental damage. The