Breadcrumb

Circuit Theory and Applications

Thermodynamic, phase diagram, and high-entropy alloys system: basic concepts

The evolution of alloy-based materials, transitioning from simple binary alloy systems to more intricate compositions, has played a pivotal role in facilitating the advancement of innovative technologies and, in turn, driving social progress. This transformative journey has been accompanied by a significant enhancement in humanity’s capacity to create novel materials. High-entropy alloys (HEAs) have emerged as a recent and noteworthy class of materials due to their novel concept and remarkable properties. These alloys exhibit exceptional mechanical characteristics, boasting impressive strength

Concept, phase selection rule, challenges, and future prospective of high-entropy alloys

High-entropy alloys (HEAs) have emerged as a promising class of materials that exhibit exceptional mechanical properties, corrosion resistance, and high-temperature stability. They have become a significant area of research in the materials science domain owing to their potential for a wide range of applications. This chapter provides an overview of the concept, phase selection rules, the challenges faced, and the future perspectives of HEAs. © 2024 Elsevier Inc. All rights are reserved including those for text and data mining AI training and similar technologies.

Characterization and properties of high-entropy alloys materials

High-entropy alloys (HEAs) are a relatively new class of materials that have been attracting significant attention in material science and engineering research. This chapter provides an introductory discourse on the microstructural characterization and properties of these fascinating materials. The term “HEAs” refers to an innovative concept of metallic materials composed of multiple principal elements, each with concentrations between 5% and 35%. Unlike conventional alloys, which typically comprise one principal element with minor alloying additions, HEAs possess a unique composition that can

A comprehensive guide to high-entropy alloy subgroups

Despite the fact that numerous equiatomic and nonequiatomic high-entropy alloys (HEAs) have been observed to form a single solid solution (SS), it has also been established that several intermediate phases can emerge, some of which exhibit the structural characteristics of intermetallic compounds (ICs) such as Laves, B2, sigma, L12, and amorphous phases. This phenomenon has been extensively documented by researchers, and it is primarily attributed to a range of competing factors, including the mixing enthalpy, mixing entropy, and disparities in atomic sizes among the constituent elements

High-Entropy Alloys: Design, Manufacturing, and Emerging Applications

High-Entropy Alloys: Design, Manufacturing, and Emerging Applications presents cutting-edge advances in the field of these materials, covering their mechanics, methods of manufacturing, and applications, all while emphasizing the link between their structure/microstructure and functional properties. The book starts with a section on the fundamentals of high-entropy alloys (HEAs), with chapters discussing their thermodynamics, subgroups (transition metal; refractory; ceramics; metallic glasses and more), physical metallurgy, and microstructural characterization. The next section features

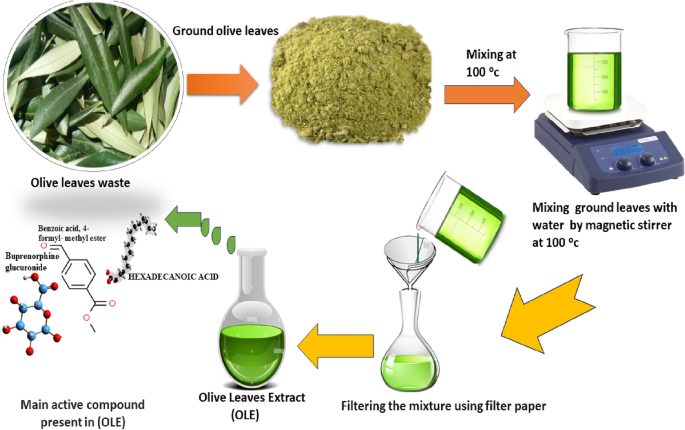

Investigation of olive leaf extract as a potential environmentally-friendly corrosion inhibitor for carbon steel

Corrosion constitutes a significant issue in industries that handle metals. Corrosion inhibitors with a low impact on the environment provide a significant economic benefit in various engineering applications. In this work, the effectiveness of olive leaves extract is evaluated as a cost-effective and environmentally-friendly corrosion inhibitor. The corrosion of carbon steel in different concentrations of hydrochloric acid (0.1, 1.0, and 2.0 M) when protected by an aqueous solution of olive leaf extract of concentrations ranging from 10 to 60 ppm is investigated. A green extraction process

Enhancing mechanical properties of Al-Zn-Mg-Cu alloys: The impact of high strain rate compression and subsequent heat treatment on microstructural evolution

This study presents a comprehensive examination of the Al-Zn-Mg-Cu alloy, focusing on the effects of high strain rate dynamic compression and heat treatment on its performance. The research aimed to understand the underlying microstructural mechanisms contributing to the enhanced mechanical properties of the alloy, which is critical for applications in aerospace and automotive industries. High strain rate dynamic compression tests, conducted at 3.0 × 1000 s−1, revealed a significant increase in both yield strength and ultimate compression strength of the Al alloy, which was accompanied by a

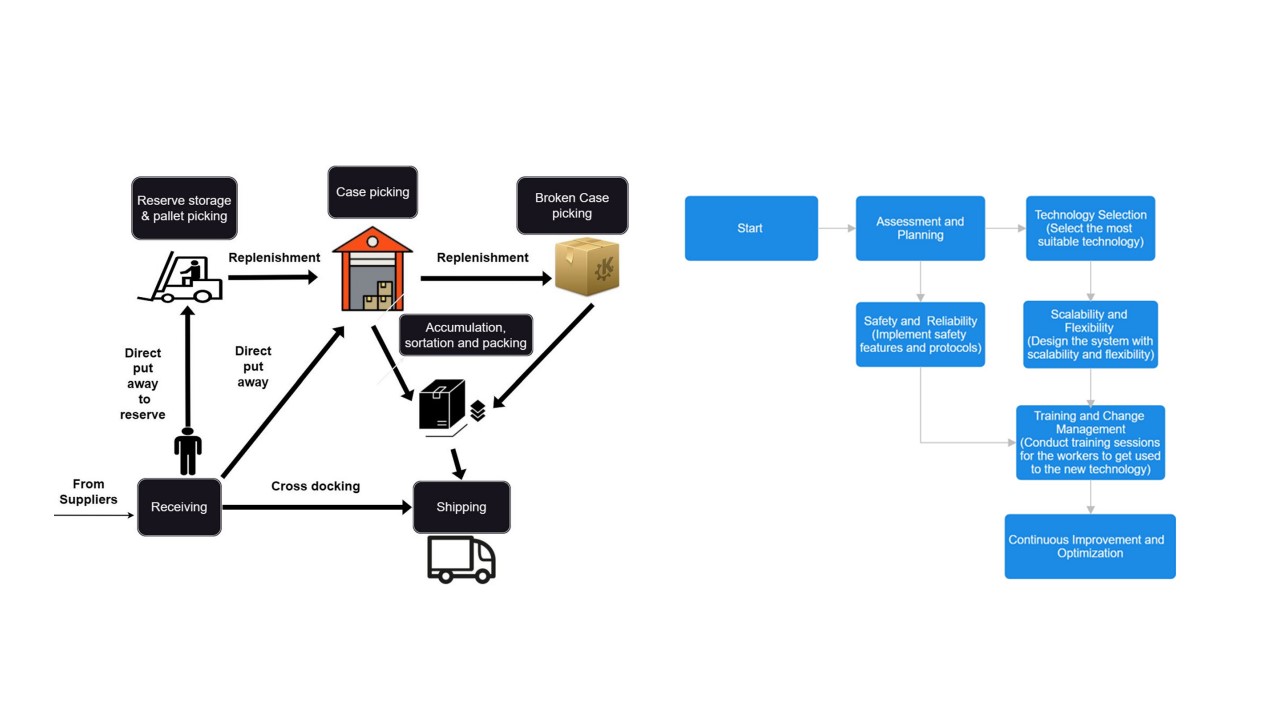

AGV and Industry 4.0 in warehouses: a comprehensive analysis of existing literature and an innovative framework for flexible automation

The just-in-time concept, mass customization, omnichannel distribution, and the rising global population have all fueled the logistics sector. Consequently, using automation inside the warehouses to make them more dynamic and sustainable for the future is one of the crucial components to adapt to this quick shift. Giants in the industry and technology are becoming more interested in the “smart warehouse” system, built with innovative warehousing technologies, as an achievable solution for the development of warehouses in the future. To contextualize the past and provide light on prospective

Waste Management Application using UML

Solid waste creation will continue to grow both in amount and pace as long as there are human activities. The consequences of improper solid waste management are highly harmful to the environment and human health, requiring immediate action to stabilize the situation. This research represents a solid waste collection management system through several unified modelling language (UML) models. The motivation for utilizing the UML modelling approach in solid waste collection management is twofold: first, the environmental importance of solid waste management collection, second the efficiency of

Implementation of process optimization to maximize line productivity in pharmaceutical industries

Abstract: Macro Group is the largest player in Egypt’s fast-growing cosmeceutical industry founded in 2002, and Macro has about 149 stock-keeping units (“SKUs”) with a 31.4% market share in 2022. The macro group has three-ampoule products for hair, namely, Atrakta, Verdex, and Solodex with an expected forecast of 134,655 FG in 2023 and it’s expected to reach 261,000 FG in 2027. 188 working days per year in 2023 are required to manufacture the forecasted units and 365 working days to manufacture 2027 forecasted units. Through observing the production line of Atrakta, it has been noticed that