Breadcrumb

Circuit Theory and Applications

Bioplastics, biodegradable plastics, and degradation in natural environments

The widespread manufacturing of traditional plastics and their use in various commercial applications endangers both fossil fuel sources and the environment. Bioplastics have emerged from the development of renewable resources to provide sustainable solutions. These polymers are more acceptable than conventional plastics because they use renewable resources such as agricultural wastes (rather than petroleum sources) and are biodegradable under various conditions. The physical and chemical structure of bioplastics significantly affects their biodegradability, and their environment plays a

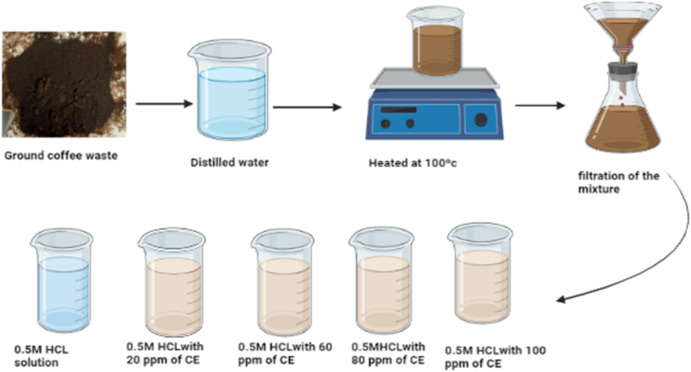

Electrochemical evaluation of green corrosion inhibitor based on ground coffee waste in Petroleum fields

Corrosion poses a significant challenge in industrial sectors that handle metallic materials. The objective of this study was to evaluate the feasibility of employing a cost-effective, organic, and eco-friendly solution derived from discarded coffee grounds, known as coffee waste extract (CE), to mitigate the corrosion rate of carbon steel in an acidic environment comprising 0.5 M hydrochloric acid (HCL) with varying concentrations ranging from 20 to 100 ppm. This research aims to explore the prospective utilization of coffee waste as an inhibitory agent that can be reutilized for diverse

Nanoionic liquid for hydrogen generation and storage

Climate change and the increase in population are encouraging many researchers to work on getting nonconventional sources of energy. Ionic liquids (ILs) have unique physicochemical properties for this field. Therefore, using nanoionic liquids and ILs in energy storage is very promising, particularly considering the reported high efficiency in the existing literature. Hydrogen production technologies have garnered considerable interest in the energy sector, particularly involving the formation of water from a petroleum field and carbon steel materials. Modern methods rely on hydrogen production

Modeling of Agile MicroFactory System using Unified Modeling Language

As the world is shedding the light on best utilization of resources, microfactory has been identified as the next big move in manufacturing. The microfactory is a small-to-medium factory that utilizes limited resources to produce flexible small batch size products. Microfactory is considered a complex agile system with integrated system components and interactions that aim to accomplish flexibility in production volume while best utilizing limited resources. Thus, modeling the microfactory considering these factors is of critical importance. The Unified Modeling Language (UML) is an effective

Lab to Industry

In terms of environmental and socio-economic benefits, the utilization of agro-fiber wastes in pulp-based product manufacturing is advantageous. Non-wood plant pulp production has shattered, and numerous non-wood fiber resources are being commercially used to make chemical pulp and paper in China, India, Latin America, Africa, the Middle East, and Turkey. Agricultural wastes, including rice and wheat straws, sorghum stalks, and annual plants like hemp and jute, are being utilized as raw materials for pulp and paper manufacture. In addition, various research has been carried out to introduce

Technological innovation in ergonomics & safety in automotive industries in Egypt

The increase in the complexity and the inspiring environment between the automotive organizations in Egypt forced the quality experts and management team to propose various tools related to Quality Management Systems but there is a slight apprehension to the ergonomic concepts in these industries. This study investigates the complications related to the ergonomics in the assembly line of an automotive company in Egypt. The assembly line is divided into several stations including trim line, chassis line and a glass handling station. The focus of this study is the ergonomics of the glass

Analysis of musculoskeletal disorders in personal care industries in Egypt

The increase in the complexity of operations in personal care industries in Egypt forced the ergonomic experts to propose various tools to analyze the human errors and eliminate the most dangerous operations according to the international standards of safety and ergonomics. International references such as the Rapid Upper Limb Assessment (RULA) and Rapid Entire Body Assessment (REBA) analysis are performed to investigate different postures as well as Computer Aided Three-Dimensional Interactive Application (CATIA) and Maynard Operation Sequence Technique (MOST softwares). A modified scissor

Methylene Blue Removal on Biodegradable Adsorptive Membranes Fabricated From Sugarcane Bagasse Pulp: Characterization and Performance Study

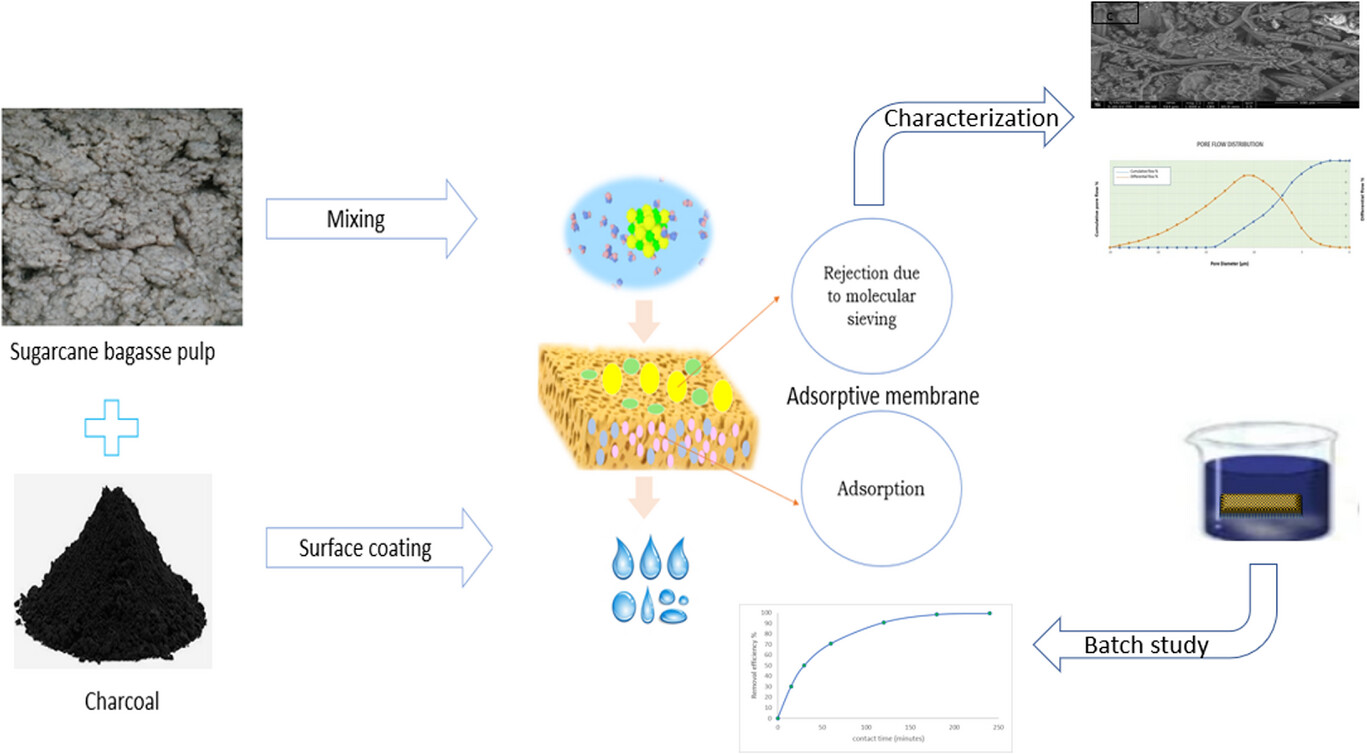

Dye-containing waste should be carefully treated using environmentally friendly technology to prevent environmental harm and preserve water resources. Adsorptive membranes are a promising new approach for decreasing, recovering, and reusing waste while also removing contaminants like dyes. In this work, two different techniques are employed to create membranes using sugarcane bagasse pulp and carbon from charcoal. In the first technique, the surface of sugarcane bagasse is coated with charcoal paste as shown in Figure 1, while in the second, the carbon is combined with sugarcane bagasse pulp

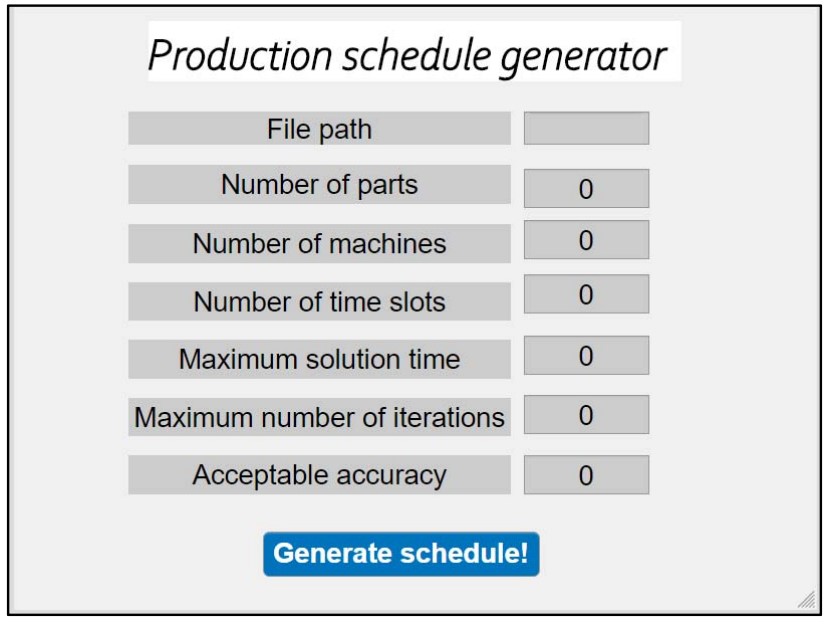

A Practical Scheduling Optimizer for Plastic Injection Molding Facilities

Scheduling of plastic injection molding facilities has been a very important issue in operations research and optimization field. This paper presents the development and experimentation of new optimization approach for production planning and scheduling. It focuses on parallel machine scheduling problems in plastic injection molding facility in Egypt. A genetic algorithm, a cuckoo search, and a mixed-integer linear programming (MILP) approach were adapted to solve the problem. Multiple experiments were conducted to compare these approaches. An improved MILP solution approach was proposed, and

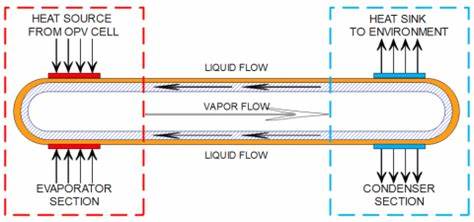

Improving the Performance of Organic Photovoltaic Panels by Integrating Heat Pipe for Cooling

A new photovoltaic technology is manufactured from an organic material that easily degrades in nature. Unfortunately, organic photovoltaics suffer from low thermal stability and lower power conversion efficiency compared with silicon-based photovoltaics. Cooling is critical in this type of photovoltaic because of these factors. This research investigates a new method to cool this organic photovoltaic with a heat pipe to achieve a minimum operating temperature and maximum temperature uniformity, the heat pipe design is fixed, and the number of cells served by a single heat pipe is studied. For