Breadcrumb

Circuit Theory and Applications

Automated multi-class skin cancer classification through concatenated deep learning models

Skin cancer is the most annoying type of cancer diagnosis according to its fast spread to various body areas, so it was necessary to establish computer-assisted diagnostic support systems. State-of-the-art classifiers based on convolutional neural networks (CNNs) are used to classify images of skin cancer. This paper tries to get the most accurate model to classify and detect skin cancer types from seven different classes using deep learning techniques; ResNet-50, VGG-16, and the merged model of these two techniques through the concatenate function. The performance of the proposed model was

An IoT Privacy-Oriented selective disclosure credential system

Personal credentials, such as passports and drivers' licenses, can be implemented electronically using multi-show protocols. In this paper, we introduce an IoT Privacy-Oriented selective disclosure credential system, i.e. based on bilinear pairings and multilinear maps. The proposed system consists of three protocols, which allow users to be in control of their personal credentials. The Credentials Authority (CA) verifies and attests to the users credentials. Once the CA signs these credentials, the users cannot modify any of them. Moreover, the users can mask these credentials in every

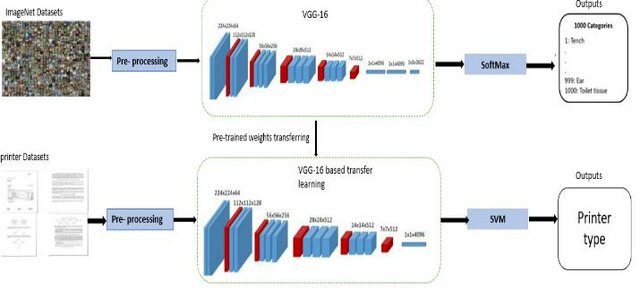

An Efficient Source Printer Identification Model using Convolution Neural Network (SPI-CNN)

Document forgery detection is becoming increasingly important in the current era, as forgery techniques are available to even inexperienced users. Source printer identification is a method for identifying the source printer and classifying the questioned document into one of the printer classes. According to what we know, most earlier studies segmented documents into characters, words, and patches or cropped them to obtain large datasets. In contrast, in this paper, we worked with the document as a whole and a small dataset. This paper uses three techniques dependent on CNN to find the

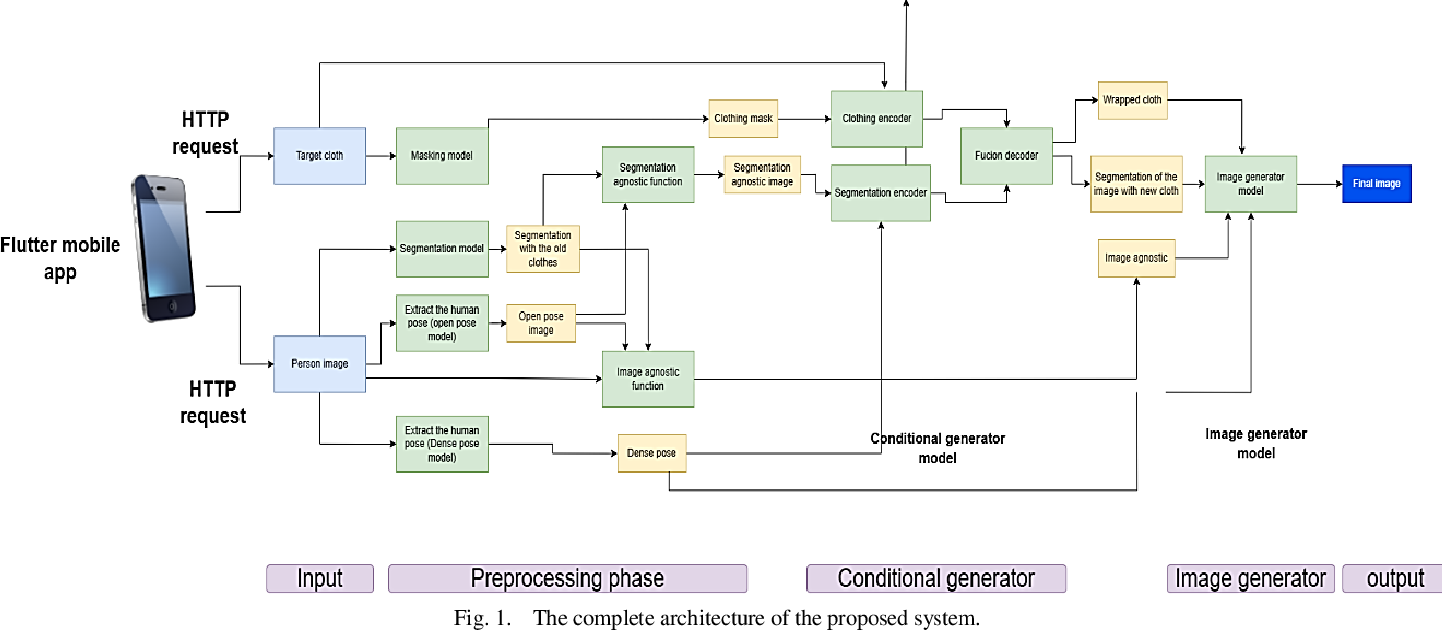

A Cost-Efficient Approach for Creating Virtual Fitting Room using Generative Adversarial Networks (GANs)

Customers all over the world want to see how the clothes fit them or not before purchasing. Therefore, customers by nature prefer brick-and-mortar clothes shopping so they can try on products before purchasing them. But after the Pandemic of COVID19 many sellers either shifted to online shopping or closed their fitting rooms which made the shopping process hesitant and doubtful. The fact that the clothes may not be suitable for their buyers after purchase led us to think about using new AI technologies to create an online platform or a virtual fitting room (VFR) in the form of a mobile

Text-Independent Algorithm for Source Printer Identification Based on Ensemble Learning

Because of the widespread availability of low-cost printers and scanners, document forgery has become extremely popular. Watermarks or signatures are used to protect important papers such as certificates, passports, and identification cards. Identifying the origins of printed documents is helpful for criminal investigations and also for authenticating digital versions of a document in today’s world. Source printer identification (SPI) has become increasingly popular for identifying frauds in printed documents. This paper provides a proposed algorithm for identifying the source printer and

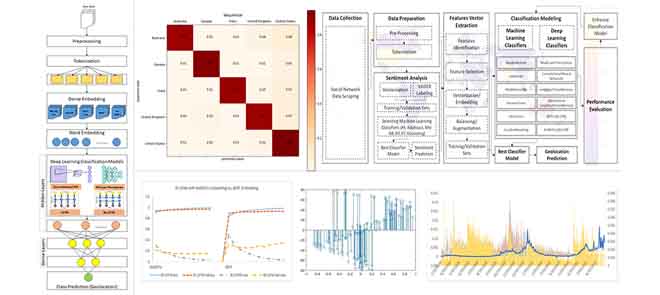

Sentiment-Based Spatiotemporal Prediction Framework for Pandemic Outbreaks Awareness Using Social Networks Data Classification

According to the World Health Organization, several factors have affected the accurate reporting of SARS-CoV-2 outbreak status, such as limited data collection resources, cultural and educational diversity, and inconsistent outbreak reporting from different sectors. Driven by this challenging situation, this study investigates the potential expediency of using social network data to develop reliable early information surveillance and warning system for pandemic outbreaks. As such, an enhanced framework of three inherently interlinked subsystems is proposed. The first subsystem includes data

Multi-Band Radio Frequency Energy Predictor for Advanced Energy Harvesting Cellular Bands Systems

Radio Frequency (RF) energy harvesting has been employed to power wireless devices. Nevertheless, RF energy harvesting encounters restrictions regarding the quantity of power it can harvest depending on signal accessibility. As a result, accurately predicting energy levels becomes crucial for enhancing the performance of energy harvesting circuits. Most research efforts have concentrated on enhancing power harvesting policies or theoretically estimating the energy obtained through RF energy harvesting. Moreover, the existing literature has primarily focused on single-band prediction approaches

Evaluating the Performance of Lightweight Block Ciphers for Resource-Constrained IoT Devices

In the context of the Internet of Things (IoT), lightweight block ciphers are of vital importance. Due to the nature of the devices involved, traditional security solutions can add overhead and perhaps inhibit the application's objective due to resource limits. Lightweight cryptography is a novel suite of ciphers that aims to provide hardware-constrained devices with a high level of security while maintaining a low physical cost and high performance. In this paper, we are going to evaluate the performance of some of the recently proposed lightweight block ciphers (GIFT-COFB, Romulus, and

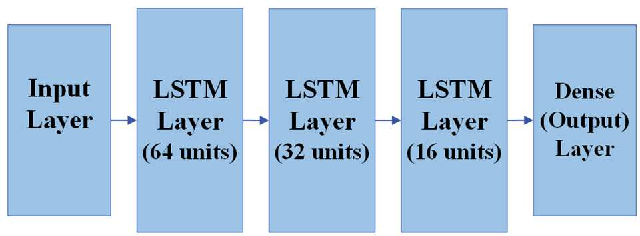

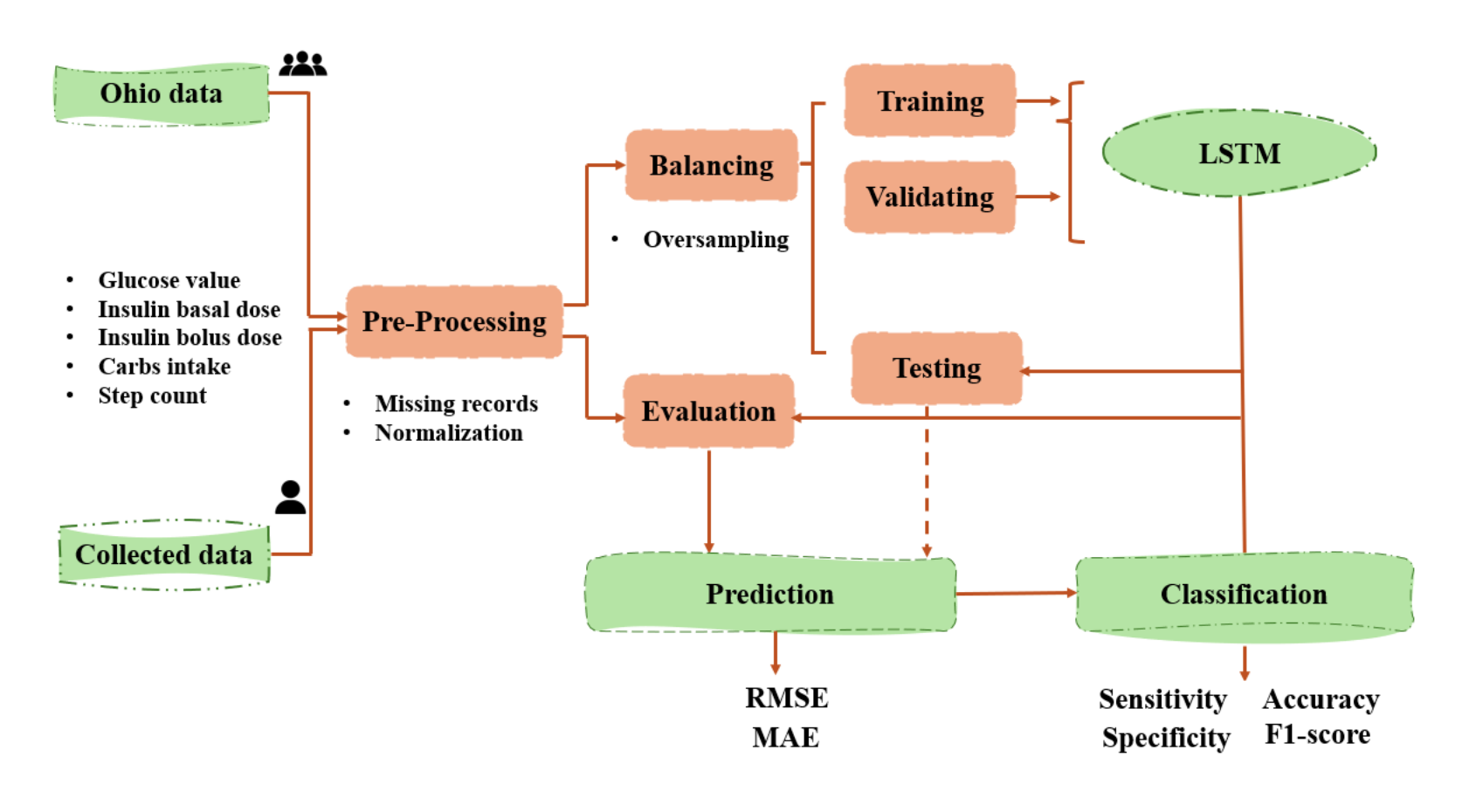

Intelligent Real-Time Hypoglycemia Prediction for Type 1 Diabetes

Hypoglycemia in Type 1 Diabetes (T1D) refers to a condition where blood glucose (BG) levels drop to abnormally low levels, typically below 70 mg/dL. This can occur when there is an excessive amount of insulin relative to the blood glucose level, leading to an imbalance that can be dangerous and potentially life-threatening if not promptly treated. The availability of large amounts of data from continuous glucose monitoring (CGM), insulin doses, carbohydrate intake, and additional vital signs, together with deep learning (DL) techniques, has revolutionized algorithmic approaches for BG

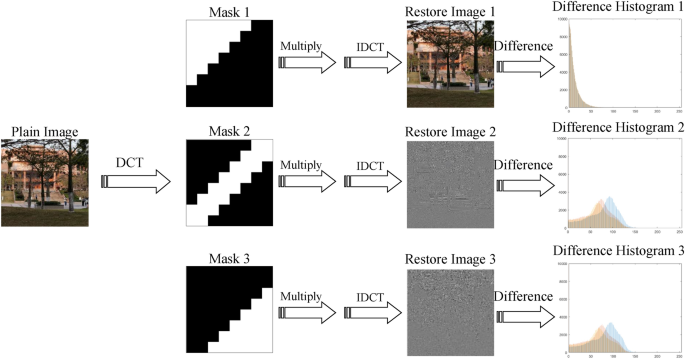

A Run-Length and Discrete Cosine Transform Based Technique for Image Splicing Detection

Digital images have emerged as the most popular means for sharing information in articles, newspapers, and even courtrooms. However, the widespread use of advanced digital imaging tools has made it easier to forge images. One such technique is image splicing, where multiple source images are merged into a single destination image to conceal or alter its content. Image splicing is an effective forgery technique, as it is difficult to detect by the naked eye. Detection of image splicing is a pattern recognition problem, based on finding image features that are sensitive to splicing. In this