Breadcrumb

Circuit Theory and Applications

A framework for smart construction contracts using BIM and blockchain

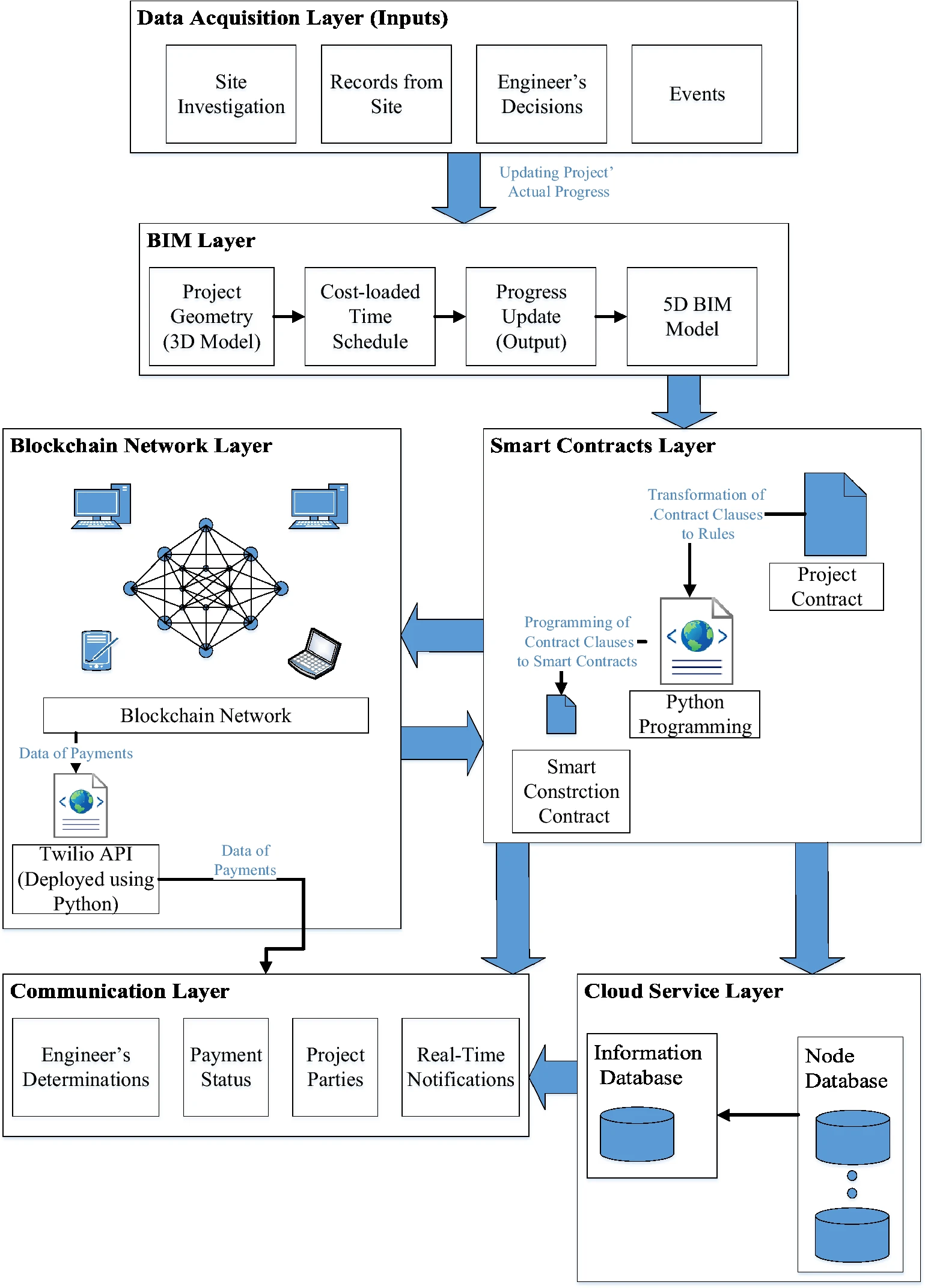

Poor payment practices are perceived as one of the biggest challenges facing the construction industry. Since payments are issued according to project contract terms, the project’s cash flow is inherently affected by the contract and how parties fulfill their obligations. This research proposes a framework for payment automation in construction projects to achieve smart construction contracts. Payments are automatically issued upon satisfying contract conditions using blockchain. Cryptocurrency is proposed to be utilized in the framework to execute the contract terms with no need for a third

Environmental feasibility of recycling construction and demolition waste

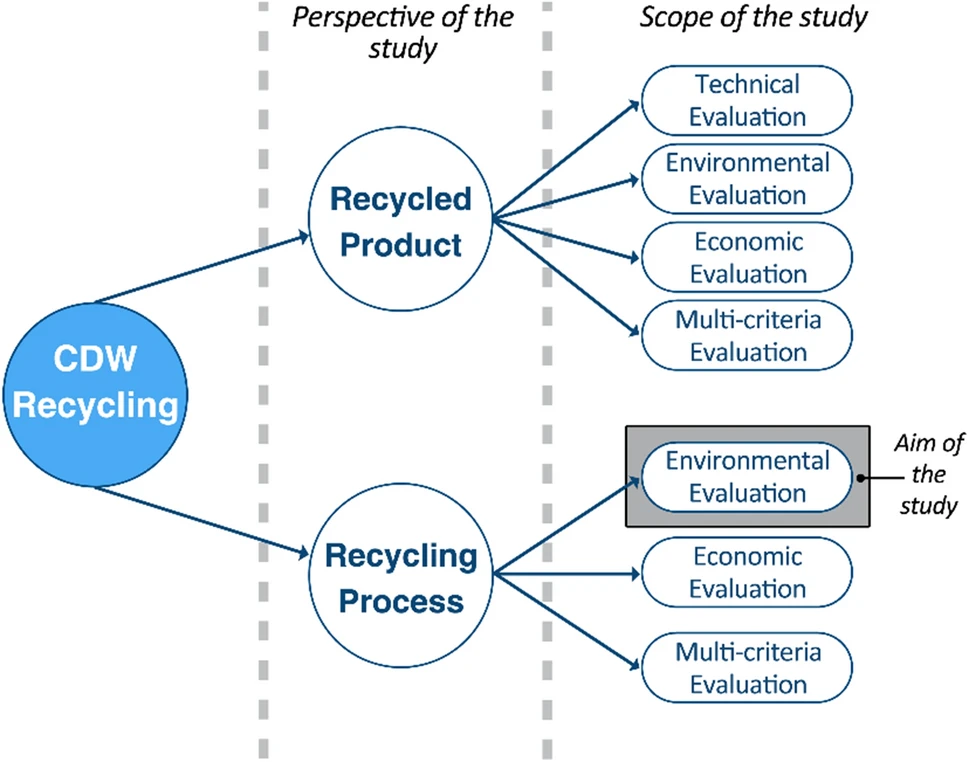

Construction, demolition, and renovation activities generate a significant amount of waste, posing serious environmental risks. The scarcity of recycling facilities makes it difficult to implement the new legislation, which calls for producing recycled aggregates. Moreover, the lack of studies on the environmental feasibility of recycling construction and demolition waste in regions with plentiful natural resources of aggregates is a contributing factor to this scarcity. Therefore, this paper studies the environmental feasibility of establishing a construction and demolition waste (CDW)

Impact assessment of implementing virtual reality in the Egyptian construction industry

Construction projects in Egypt are becoming more complex as the need for mega projects increases to meet the Egyptian 2030 vision. Meanwhile, the advancement of Virtual Reality technologies is apparent in the 21st century. This paper aims to assess the impact of implementing virtual reality in the Egyptian construction industry. An application using Fuzor VDC and Oculus Quest 2 has been developed elaborating the technology's use. The application includes 4D simulation and meetings in virtual reality. Furthermore, a survey is conducted to measure the impact of implementation on key project

LRFD for Shallow Foundations Using Plate Load Test Data

In this study, a database was developed to house reliable results from 43-plate load tests conducted on different types of compacted soil, including load-displacement responses and other information about soil and testing conditions. Using information from that database, resistance factors were developed for shallow foundations based on the prevalent first order second moment reliability approach. The resistance factors were calculated for common equations used to calculating the soil bearing capacity such as Terzaghi, Meyerhof, and Hansen. The calibration was based on comparing the calculated

The Psychological Impact of University Brand Equity Using Firm Generated EWOM on Students’ Satisfaction: The Moderating Effect of Gender

This study uses firm-generated "electronic word of mouth (eWOM)" and students' satisfaction to analyse the effect of university brand equity. Four aspects of brand equity—"awareness, positioning, perceived quality, and trustworthiness"—are examined by the conceptual framework. It also examines how gender influences the relationship between student satisfaction and institution brand equity. At Nile University in Cairo, Egypt, the study used an exploratory survey methodology with a sample of 295 students from its four schools of "business administration, computer science, engineering, and

Organizational learning via gamification for employer brand management

Purpose: This paper aims to deepen our understanding of how serious games could be used for learning in organizations to empower brand performance and image sustaining competitive advantage from a Resource Based View (RBV) perspective and to examine the practical implications of the evolving technologies for employers. Design/methodology/approach: The research methodology is based on a qualitative approach adopting the case study research method (Yin, 2003). Data were collected through fifteen semi-structured interviews (a total of twelve hours) with the involved departments (particularly

Impact of working while studying on university students’ academic performance in Egypt during the COVID-19 pandemic and transition to online learning

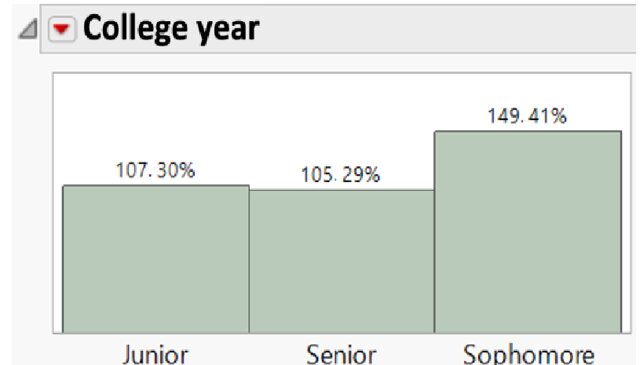

In the context of online education, which has been growing as a common approach, this paper examines the impact of working while studying on university students’ academic performance, namely Cumulative GPA (CGPA), as a rising trend in Egypt, especially after the pandemic and the shift into online learning. The research followed an exploratory survey method, namely a quantitative approach, with a sample of 361 students randomly selected using the convenience sampling method from a total of 3326 students, both working and non-working, from years 2 to 4 across the four schools at Nile University

A Proposed Nonlinear Programming Optimization Model for Optimal Budget Mix of Digital Marketing Campaigns

This paper proposes a nonlinear mathematical model to address the problem of optimizing budget allocation within digital marketing campaigns. The model provides marketers with a systematic quantitative framework for effective budget allocation across various platforms. The model seeks to identify the optimal budget mix that maximizes the expected net impressions using the Sainsbury Normal Method (SNM). The proposed model considers multiple constraints, such as budget limitations and advertiser's preferences. Results demonstrate the applicability of the model through hypothetical two case

Veiled on Instagram? Representation of Veiled versus Nonveiled Women in Western and Egyptian Instagram Posts

This study uses visual, quantitative content analysis to examine whether there is a significant difference in the representation of veiled versus nonveiled women in branded Instagram posts. We also tested the representation of women in Western and Egyptian branded Instagram posts. We used a sample of 200 branded Instagram posts created to promote products and services. The study tested five categories based on Goffman’s and then Kang’s gender analysis models: feminine touch, ritualization of subordination, licensed withdrawal, body display, and independence. We report a significant difference

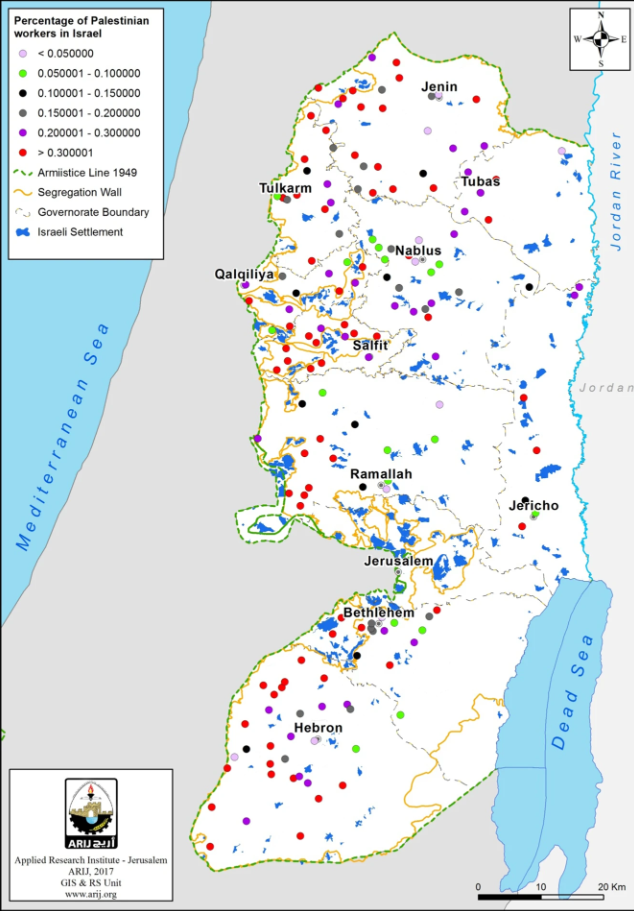

The effects of a negative economic shock on male marriage in the West Bank

This study examines how a large negative economic shock impacts marriage rates for young men in the West Bank. Utilizing data from before and after the sudden and abrupt closure of the Israeli labor market for Palestinian commuters from the West Bank in 2001, our empirical design employs a difference-in-difference strategy and uses the variations in localities’ exposure to the Israeli labor market before the shock. The closure reduced the employment and income of adult men asymmetrically across localities. Our findings show that the closure caused a reduction in marriage rates among young men