Numerical Simulations and FPGA Implementations of Fractional-Order Systems Based on Product Integration Rules

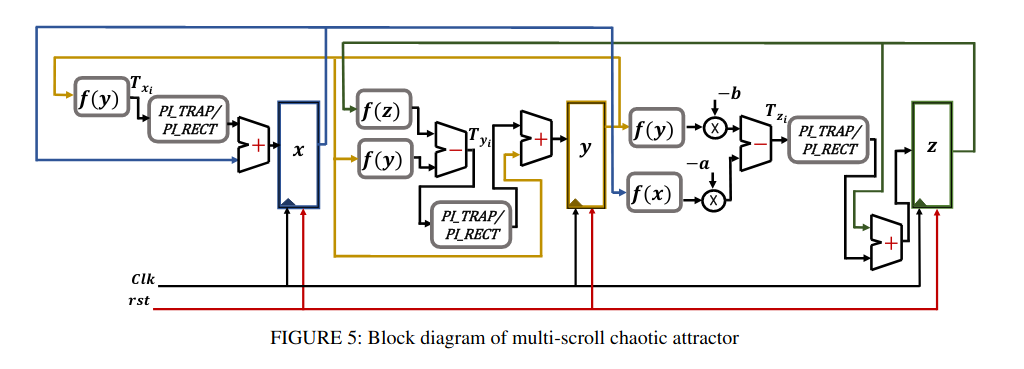

Product integration (PI) rules are well known numerical techniques that are used to solve differential equations of integer and, recently, fractional orders. Due to the high memory dependency of the PI rules used in solving fractional-order systems (FOS), their hardware implementation is very difficult and resources-demanding. In this paper, modified versions of the PI rules are introduced to facilitate their digital implementations. The studied rules are PI rectangular, PI trapezoidal, and predict-evaluate-correct-evaluate (PECE) rules. The three modified versions of the PI rules are validated using a benchmark system of differential equations for different sizes of the memory window to show the effect of the window size on the solution accuracy. Additionally, the three modified versions of the PI rules are used to simulate a novel fractional-order chaotic system (FOCS) where its bifurcation diagrams are discussed with the window length parameter. The chaotic system is then implemented on a Field Programmable Gate Array (FPGA). There are only a few trials in literature to implement the fractional PECE algorithm on FPGA, nevertheless, the proposed FPGA realization is compared with the most recent of these trials. The FPGA implementations of the three PI rules are made using Xilinx ISE 14.7 on Artix 7 kit. The achieved throughput are 1280 Mbits/sec for PI rectangular, 128.8 Mbits/sec for PI trapezoidal, and 129.12 Mbits/sec for fractional-order PECE. © 2013 IEEE.