Breadcrumb

Circuit Theory and Applications

A Framework for Reporting Ergonomic Sitting Posture Anomalies

Application of ergonomics' rules has become a necessity in today's world. Due to the lack of knowledge of what these rules are and the resources needed to fund them, a lot of people develop health issues. One of the most common health issues relate to sitting in a wrong posture for extended period.In this document, a framework that can help in minimizing the existence of the sitting posture anomaly is proposed. This framework takes into account using limited resources as well as being able to apply it in a home environment. © 2022 IEEE.

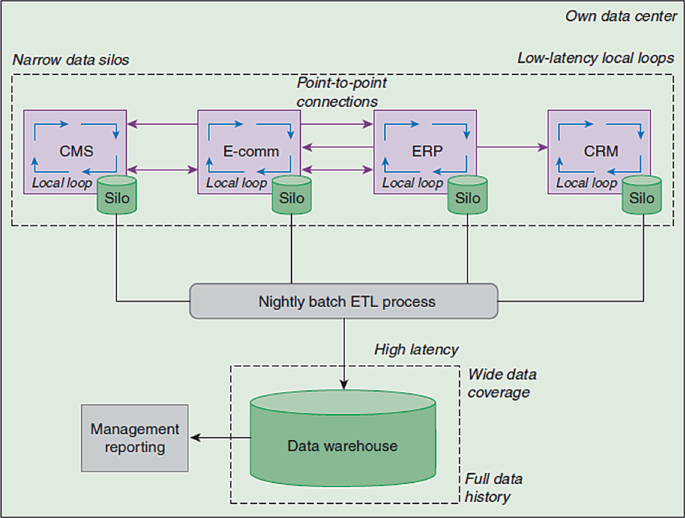

Walk Through Event Stream Processing Architecture, Use Cases and Frameworks Survey

Nowadays events stream processing is one of the top demanding field(s) because of the business urgent need for ongoing real time analytics & decisions. Most business domains avail huge amount of data aiming to make use of each data point efficiently. Corporate(s) have a cloud of events vary from internal business transactions, social media feeds, IoT devices logs,.. etc. In this paper we would discuss state of the art event stream processing technologies using cloud of events by summarizing event stream processing definition, data flow architectures, common use cases, frameworks and

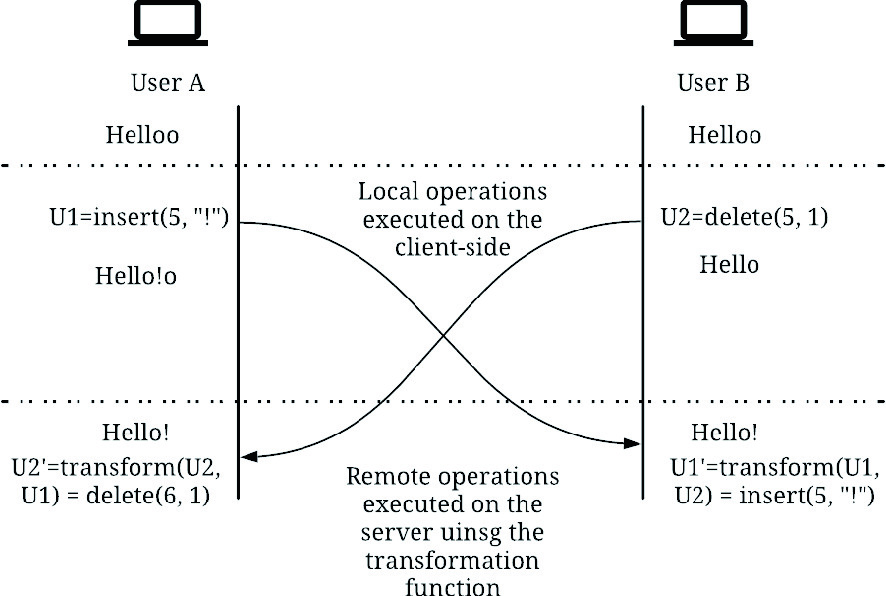

A Survey of Concurrency Control Algorithms in Collaborative Applications

Collaborative applications are becoming more prevalent for a variety of reasons, most important of which is the increased interest in remote work. In addition to adapting the business processes to a remote setting, designers of collaborative software have to decide on how their software can be used collaboratively. This paper discusses the two main technologies used to enable network-based real- or near-real-time collaborative software, namely Operational Transformation and Conflict-free Replicated Data Types. Recent developments in each technology are discussed, as well as a brief overview of

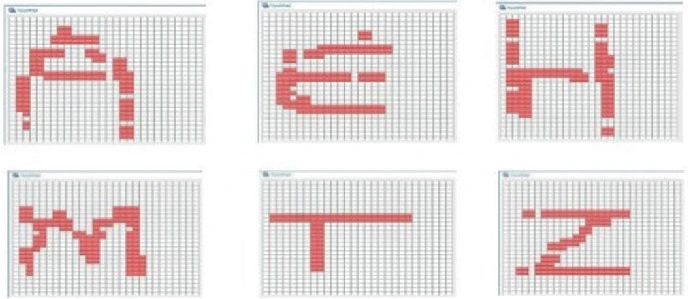

Handwriting Letter Recognition on the Steering Wheel Switches

Automotive steering wheel switches technologies are evolving to give easy access to the several interior or exterior functions. This is worth a deep analysis for the current trends in order not to become unintuitive for the driver due to the increasing number of buttons. Through different technologies particularly the capacitive ones, range of innovative solutions have been developed like reconfigurable buttons on the steering wheel to offer commanding several functions twice or triple the number of allocated push buttons. In this paper, we address the problem in a different freely way to

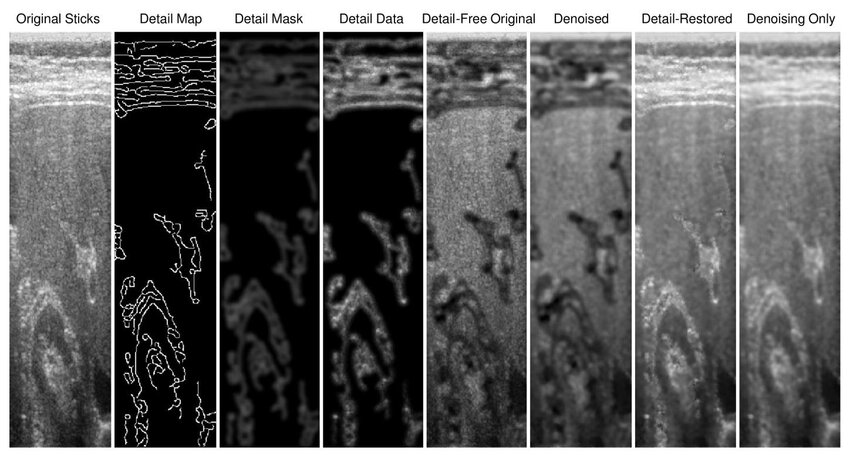

Edge Detail Preservation Technique for Enhancing Speckle Reduction Filtering Performance in Medical Ultrasound Imaging

—Ultrasound imaging is a unique medical imaging modality due to its clinical versatility, manageable biological effects, and low cost. However, a significant limitation of ultrasound imaging is the noisy appearance of its images due to speckle noise, which reduces image quality and hence makes diagnosis more challenging. Consequently, this problem received interest from many research groups and many methods have been proposed for speckle suppression using various filtering techniques. The common problem with such methods is that they tend to distort the edge detail content within the image and

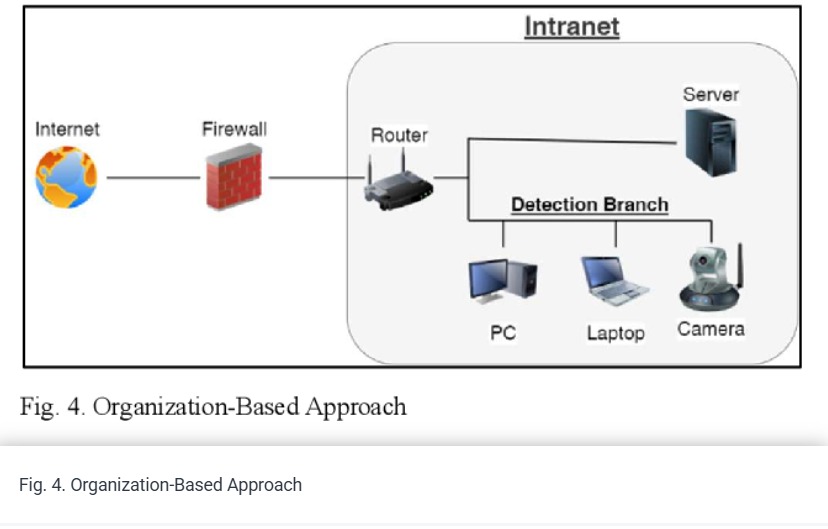

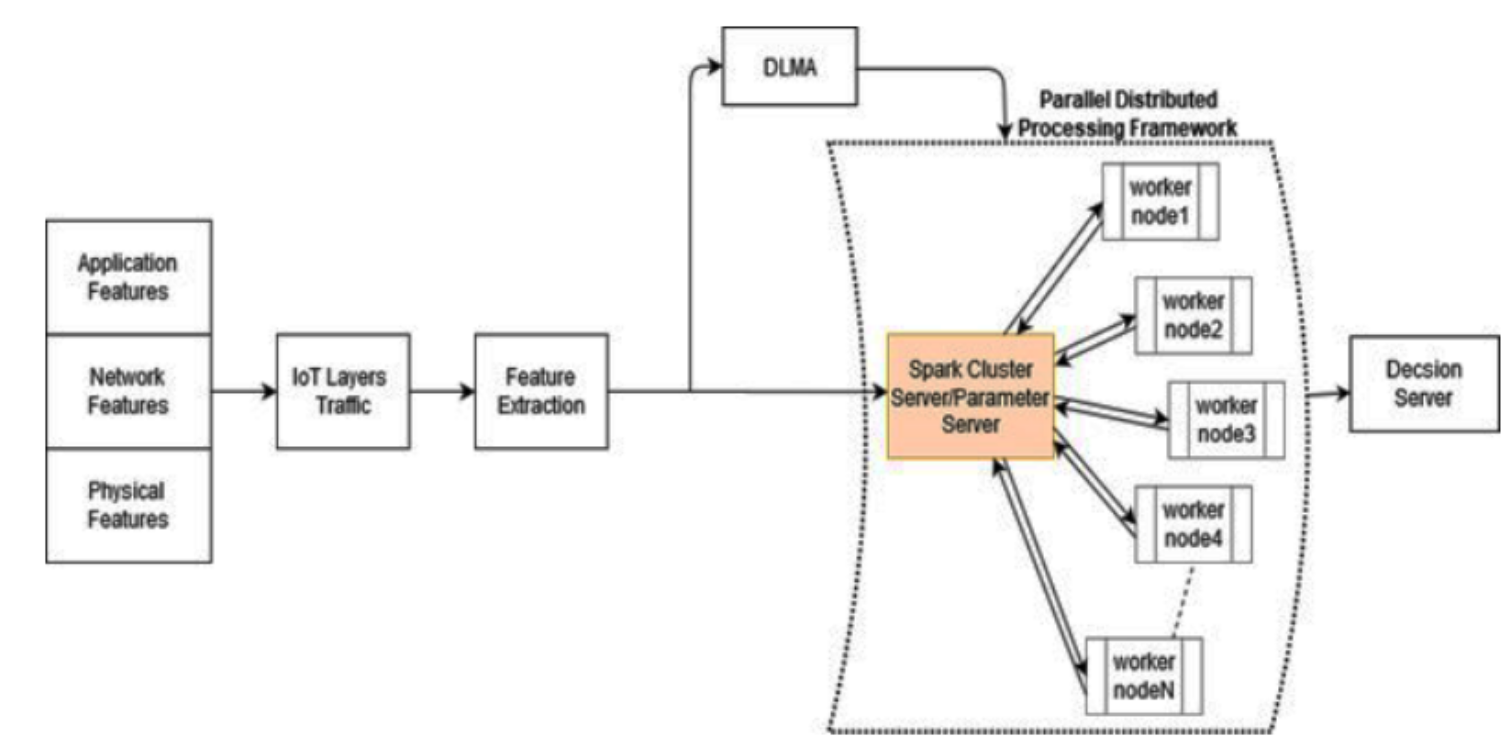

Cross-Layer Distributed Attack Detection Model for the IoT

The security of IoT that is based on layered approaches has shortcomings such as the redundancy, inflexibility, and inefficiently of security solutions. There are many harmful attacks in IoT networks such as DoS and DDoS attacks, which can compromise the IoT architecture in all layers. Consequently, cross layer approach is proposed as an effective and practical security defending mechanism. Cross-layer distributed attack detection model (CLDAD) is proposed to enhance security solutions for IoT environments. CLDAD presents a general detection method of DDoS in sensing layer, network layer, and

Ibn Sina: A patient privacy-preserving authentication protocol in medical internet of things

The prosperous advancement in Medical Internet of Things (MIoT) technologies has hastened the development of healthcare systems. MIoT improves the traditional medical facilities through periodically monitor of patient's health records. Electronic Medical Records (EMRs) are sensitive private data and needs efficient secure and private schemes that interchange these EMRs between healthcare providers and patients. Most of the current privacy preserving schemes do not provide the desired privacy level and suffer from computation and communication overheads. The length of an IDentity-based Strong

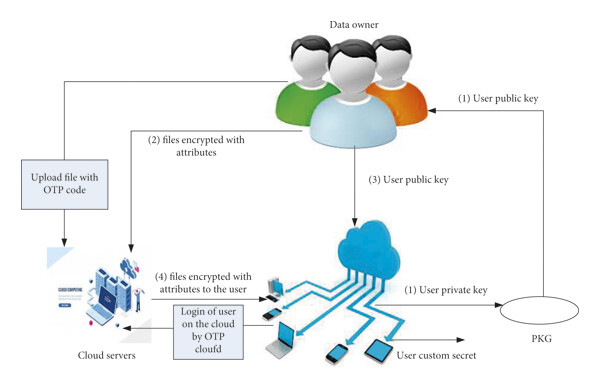

A New Secure Model for Data Protection over Cloud Computing

The main goal of any data storage model on the cloud is accessing data in an easy way without risking its security. A security consideration is a major aspect in any cloud data storage model to provide safety and efficiency. In this paper, we propose a secure data protection model over the cloud. The proposed model presents a solution to some security issues of cloud such as data protection from any violations and protection from a fake authorized identity user, which adversely affects the security of the cloud. This paper includes multiple issues and challenges with cloud computing that

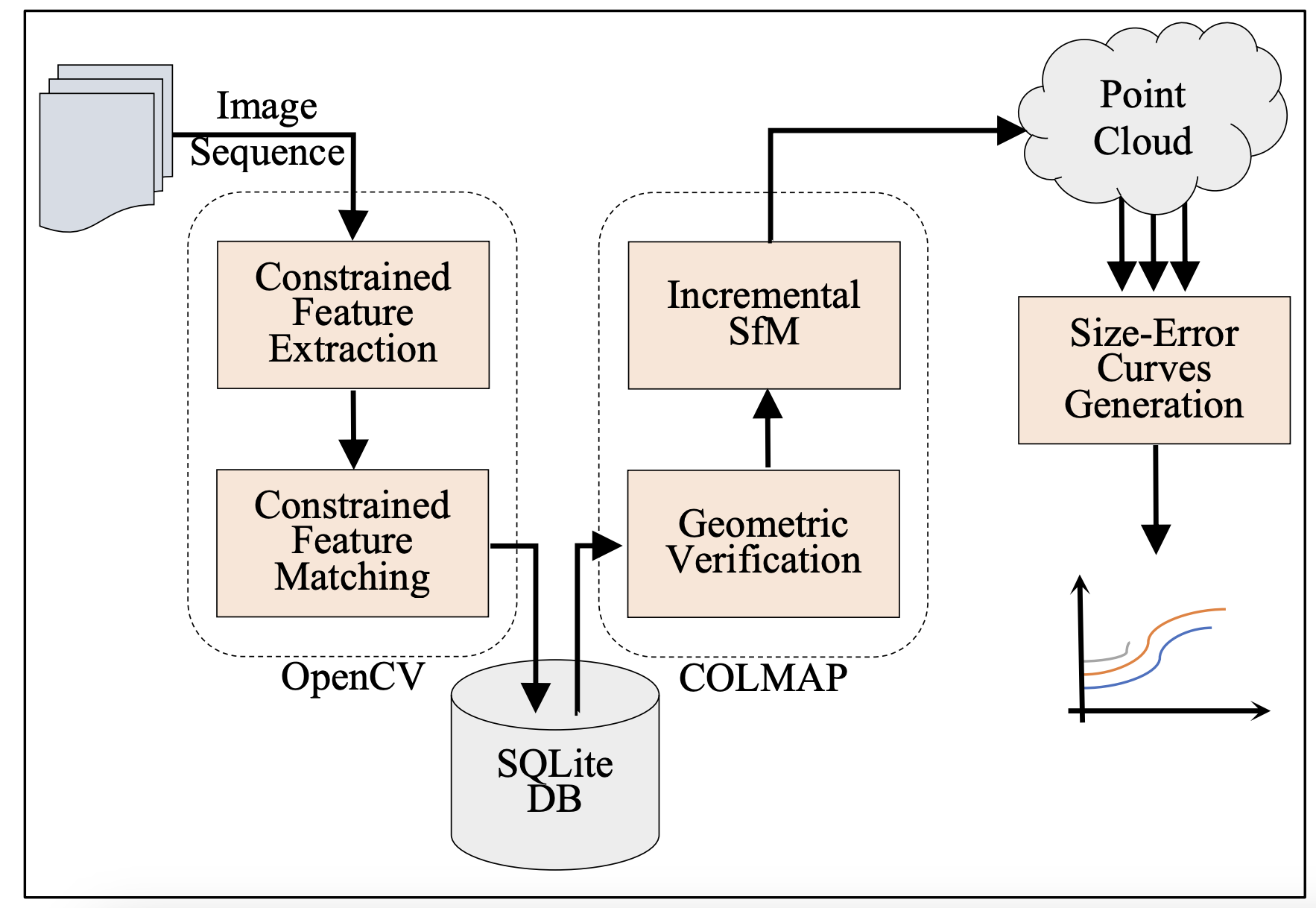

Towards a Fair Evaluation of Feature Extraction Algorithms Robustness in Structure from Motion

Structure from Motion is a pipeline for 3D reconstruction in which the true geometry of an object or a scene is inferred from a sequence of 2D images. As feature extraction is usually the first phase in the pipeline, the reconstruction quality depends on the accuracy of the feature extraction algorithm. Fairly evaluating the robustness of feature extraction algorithms in the absence of reconstruction ground truth is challenging due to the considerable number of parameters that affect the algorithms' sensitivity and the tradeoff between reconstruction size and error. The evaluation methodology

Detection and Prediction of Future Mental Disorder From Social Media Data Using Machine Learning, Ensemble Learning, and Large Language Models

Social media platforms are used widely by all people to express their feelings, opinions, and emotional states. Billions of people worldwide use them daily to share what they think and feel in their posts. Amongst all social media available platforms, Facebook only contains around three billion personal accounts. In this work Reddit dataset is used to automatically detect mental illness from social media posts. This study is not only limited to early detection of already existing mental illness or disorder like depression and anxiety from social posts, but also and most importantly the study