Breadcrumb

Circuit Theory and Applications

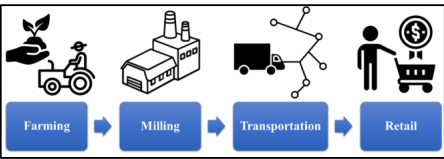

Scenario Analysis for Supply Chain Management of Milled Grain Products in South Africa: A System Dynamics Approach

This study aimed to identify the interactions between the sub-systems of the supply chain system of milled grain products, in South Africa, namely: (1) farming (agricultural); (2) transport (transportation); (3) manufacturing (milling); and (4) trade (retail). Furthermore, this paper investigated how these sub-systems are affected by economic and natural external factors namely: (1) the exchange rate between ZAR and USD; (2) the price of international crude oil; and (3) climate change and/or droughts. For this purpose, system dynamics (SD) model was developed and used, which enabled to

Measuring the efficiency of banks using high-performance ensemble technique

The importance of technology and managerial risk management in banks has increased due to the financial crisis. Banks are the most affected since there are so many of them with poor financial standing. Due to this problem, an unstable and inefficient financial system causes economic stagnation in both the banking sector and overall economy. Data envelopment analysis (DEA) has been used to examine decision-making units (DMUs) performance to enhance efficiency. Currently, with the rapid growth of big data, adding more DMUs will likely require a large amount of memory and CPU time on the computer

Some universal patterns in income distribution: An econophysics approach

The econophysics “two-class” approach yields a novel theoretical and empirically robust relation: The per capita income (Formula presented.) of any bottom fraction (x) of the population equals a(x)∙(1−G) (Formula presented.), where a(x) is a coupling coefficient, G the Gini, and (Formula presented.) is national per capita income. For the bottom 70%, a(70) = 1, which yields the Sen inequality adjustment to the 1993 UNDP Human Development Index, without any reliance on social welfare functions. Alternately, a(80) = 1.1 yields the bottom 80% per capita income (Vast Majority Income). We propose

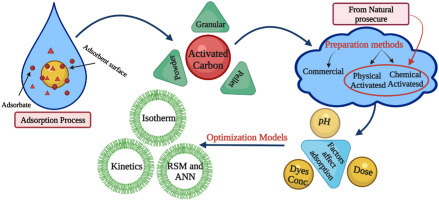

Adsorption as an Emerging Technology and Its New Advances of Eco-Friendly Characteristics: Isotherm, Kinetic, and Thermodynamic Analysis

Water contamination with paints causes a colour agent to the water that negatively affects the environment, organisms, and humans. Different physicochemical processes are applied for wastewater treatment; however, they have many drawbacks such as high cost, generating toxic waste, and non-effective at low concentrations. Adsorption is considered a promising technique for pollutant removal from polluted wastewater. Commercial activated carbon, nano-materials, and natural biological materials are used as adsorbents in adsorption. This chapter focuses on discussing the adsorption process, the

Water Importance and Pollution Sources-Recommended Limits of Pollutants

There are many water resources like rivers, seas, rains, and groundwater, which can be used in different sectors such as agricultural, domestic, and industrial uses. Therefore, different wastewater effluents with different properties are produced depending on their source. Industrial wastewater is one of the most harmful effluents due to the presence of toxic pollutants such as heavy metals, dyes, and other toxic substances. Usually, water is used in different industries for different internal processes, and then the resulting wastewater is discharged without treatment into the water resources

Review of activated carbon adsorbent material for textile dyes removal: Preparation, and modelling

Water contamination with colours and heavy metals from textile effluents has harmed the ecology and food chain, with mutagenic and carcinogenic effects on human health. As a result, removing these harmful chemicals is critical for the environment and human health. Various standard physicochemical and biological treatment technologies are used; however, there are still some difficulties. Adsorption is described as a highly successful technology for removing contaminants from textile-effluents wastewater compared to other methods. Several adsorbent materials, including nanomaterials, natural

Applied Techniques for Wastewater Treatment: Physicochemical and Biological Methods

Polluted water is one of the significant challenges facing the world nowadays, especially with the noticed water shortage recorded in the last period. Different treatment methods, physicochemical and biological, were presented for pollutant removal from polluted wastewater. This review discusses the treatment methods starting from the biological part to help reduction of organics, which are solids that appear in the wastewater. After that, the physicochemical techniques will be discussed as a second part of the treatment process to minimize the heavy metal, dyes, and other pollutants

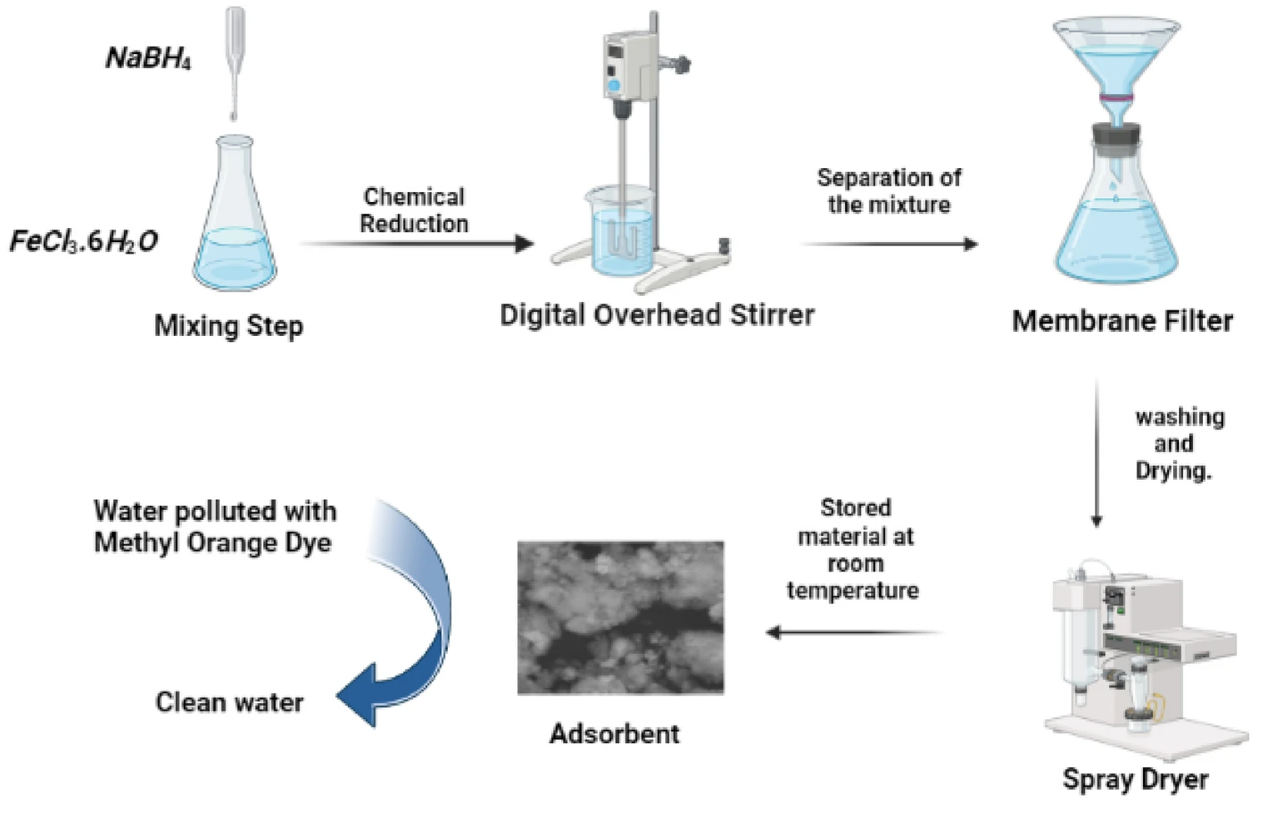

Preparation and Characterization of nZVI, Bimetallic Fe 0-Cu, and Fava Bean Activated Carbon-Supported Bimetallic AC-F e 0-Cu for Anionic Methyl Orange Dye Removal

Early detection of hypo/hyperglycemia using a microneedle electrode array-based biosensor for glucose ultrasensitive monitoring in interstitial fluid

Diabetes is a common chronic metabolic disease with a wide range of clinical symptoms and consequences and one of the main causes of death. For the management of diabetes, painless and continuous interstitial fluid (ISF) glucose monitoring is ideal. Here, we demonstrate continuous diabetes monitoring using an integrated microneedle (MN) biosensor with an emergency alert system. MNs are a novel technique in the field of biomedical engineering because of their ability to analyze bioinformation with minimal invasion. In this work we developed a poly(methyl methacrylate) (PMMA) based MN glucose

Integrated Analysis of Bulk and Single-Cell Transcriptomics in Cervical Cancer: Insights into BPGM, EGLN3, and SUN1

Cervical cancer (CC) is considered a significant global health threat to women therefore there is a need for personalized treatment strategy based on individual-specific gene expression patterns to enhance recovery and survival rates. Although a few studies have linked bisphosphoglycerate mutase (BPGM) expression with CC, its precise role in CC progression remains unclear. In this study, we conducted an integrated analysis for both bulk and single-cell RNA sequencing data to investigate the involvement of BPGM in CC. On the bulk RNA level, the Wilcoxon test result showed a significant