Breadcrumb

Circuit Theory and Applications

Pseudo Random Number Generators Employing Three Numerical Solvers of Chaotic Generators

Pseudo-Random Number Generator (PRNG) is required for various applications, especially cryptography. PRNGs are employed in symmetric-key algorithms, where a single key is used as a seed to the PRNG to generate a sequence of random numbers that are employed to encrypt and decrypt certain data. This work proposes a PRN G system that employs the time series generated from the numerical solution of systems of chaotic-generators Differential Equations (DEs) utilizing three different DEs solvers; Euler, Runge-Kutta 4th order, and Runge-Kutta 5th order. Various systems were solved using each of the

Sentiment Analysis: Amazon Electronics Reviews Using BERT and Textblob

The market needs a deeper and more comprehensive grasp of its insight, where the analytics world and methodologies such as 'Sentiment Analysis' come in. These methods can assist people especially 'business owners' in gaining live insights into their businesses and determining wheatear customers are satisfied or not. This paper plans to provide indicators by gathering real world Amazon reviews from Egyptian customers. By applying both Bidirectional Encoder Representations from Transformers 'Bert' and 'Text Blob' sentiment analysis methods. The processes shall determine the overall satisfaction

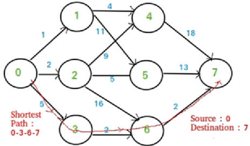

Comparison of Parallel and Serial Execution of Shortest Path Algorithms

Shortest Path Algorithms are an important set of algorithms in today's world. It has many applications like Traffic Consultation, Route Finding, and Network Design. It is essential for these applications to be fast and efficient as they mostly require real-Time execution. Sequential execution of shortest path algorithms for large graphs with many nodes is time-consuming. On the other hand, parallel execution can make these applications faster. In this paper, three popular shortest path algorithms-Dijkstra, Bellman-Ford, and Floyd Warshall-Are both implemented as serial and parallel programs

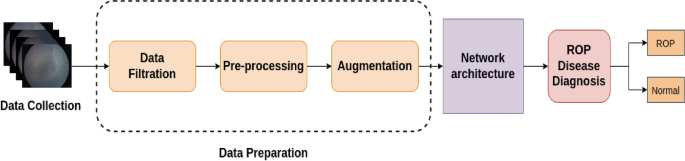

A Robust Deep Learning Detection Approach for Retinopathy of Prematurity

Retinal retinopathy of prematurity (ROP), an abnormal blood vessel formation, can occur in a baby who was born early or with a low birth weight. It is one of the primary causes of newborn blindness globally. Early detection of ROP is critical for slowing and stopping the progression of ROP-related vision impairment which leads to blindness. ROP is a relatively unknown condition, even among medical professionals. Due to this, the dataset for ROP is infrequently accessible and typically extremely unbalanced in terms of the ratio of negative to positive images and the ratio of each stage of it

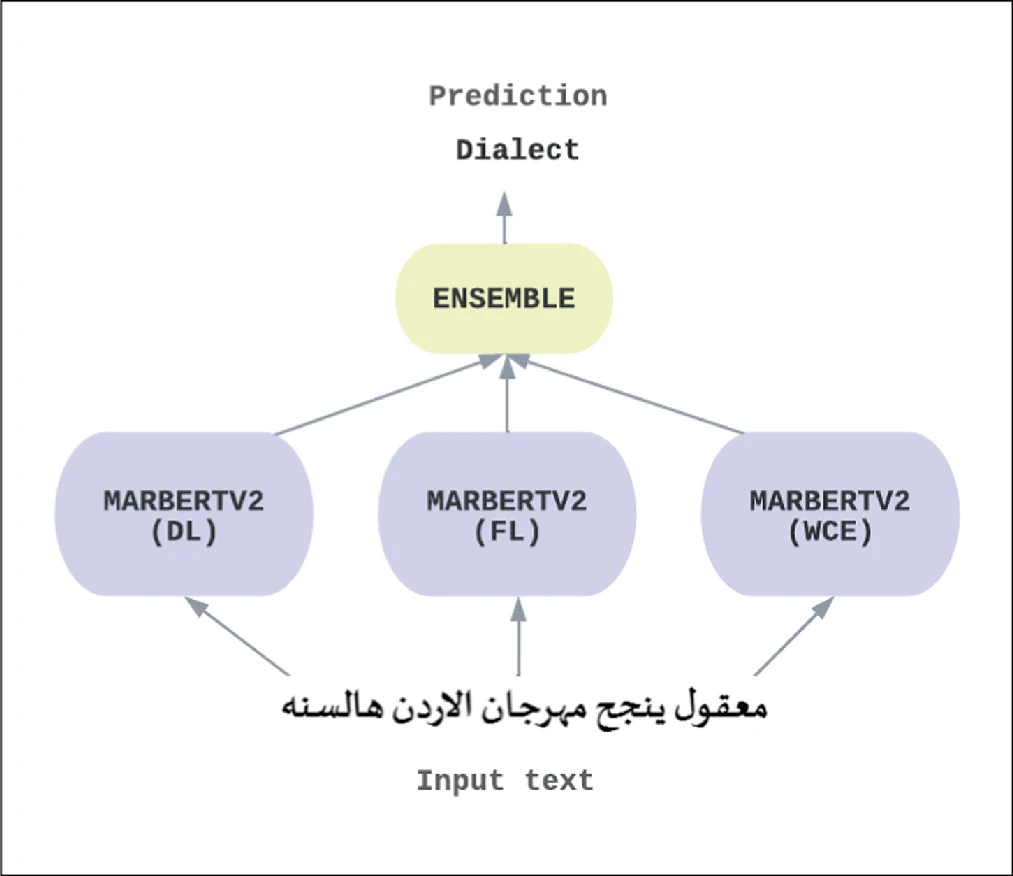

In the Identification of Arabic Dialects: A Loss Function Ensemble Learning Based-Approach

The automation of a system to accurately identify Arabic dialects many natural language processing tasks, including sentiment analysis, medical chatbots, Arabic speech recognition, machine translation, etc., will greatly benefit because it’s useful to understand the text’s dialect before performing different tasks to it. Different Arabic-speaking nations have adopted various dialects and writing systems. Most of the Arab countries understand modern standard Arabic (MSA), which is the native language of all other Arabic dialects. In this paper we propose a method for identifying Arabic dialects

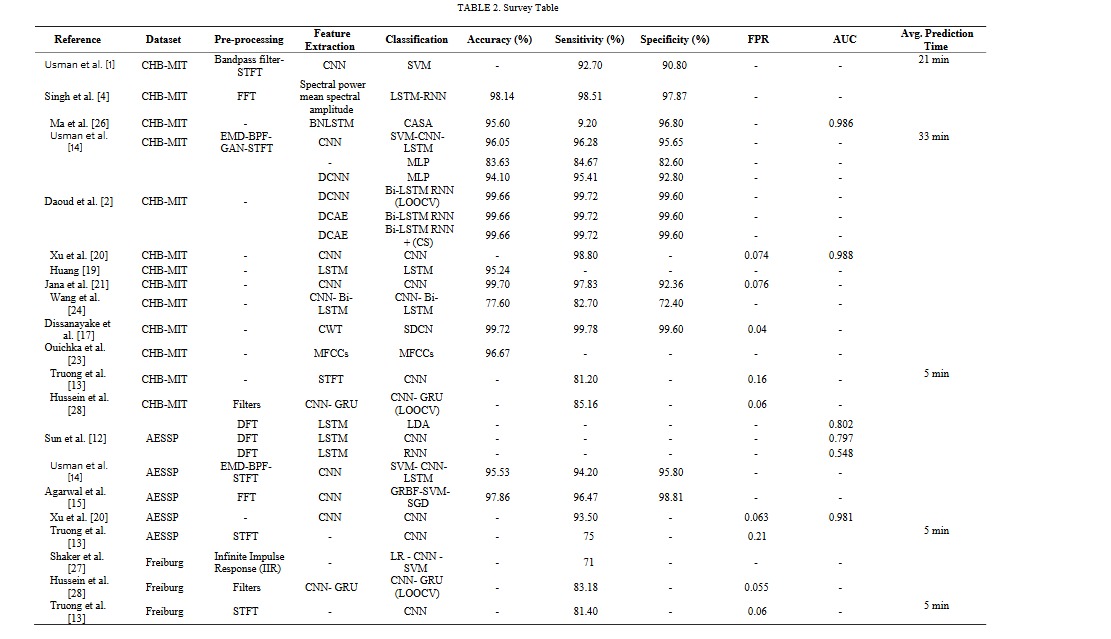

Deep Learning Approaches for Epileptic Seizure Prediction: A Review

Epilepsy is a chronic nervous disorder, which disturbs the normal daily routine of an epileptic patient due to sudden seizure onset that may cause loss of consciousness. Seizures are periods of aberrant brain activity patterns. Early prediction of an epileptic seizure is critical for those who suffer from it as it will give them time to prepare for an incoming seizure and alert anyone in their close circle of contacts to aid them. This has been an active field of study, powered by the decreasing cost of non-invasive electroencephalogram (EEG) collecting equipment and the rapid evolution of

Light-Weight Food/Non-Food Classifier for Real-Time Applications

Today, automatic food/non-food classification became extremely important for many real-time applications, specifically since the pandemic of the COVID-19 virus. Such that the 'no food policy' now became applied more than ever to help decrease the spread of the COVID-19 virus. Consequently, many studies used deep neural networks for the food/non-food classification task, yet these deep neural networks were computationally expensive. As a result, in this paper, a lightweight Convolution Neural Network (CNN) is proposed and put into use for classifying foods and non-foods. Compared to prior

Light-Weight Food Image Classification For Egyptian Cuisine

Food is an integral aspect of daily life in all cultures. It highly affects people's diets, eating behaviors, and overall health. People with poor eating habits are usually overweight or obese, which leads to chronic diseases such as diabetes and cardiovascular disease. Today, the classification of food images has several uses in managing medical conditions and dieting. Deep convolutional neural network (DCNN) architectures provide the foundation for the most recent food recognition models. However, DCNNs are computationally expensive due to high computation time and memory requirements. In

Light-Weight Intelligent Egyptian Food Detector For Diabetes Management

Diabetic patients need a management tool that combines multiple features and tracks and views detailed data time-efficiently. Effective food logging is an important element of health monitoring. In this paper, we propose 'Suger.ly', a lightweight mobile application with artificial intelligence food recognition for diabetes management. The system has been trained to recognize 101 distinct types of food, with a focus on Egyptian cuisine. The app can then get nutritional value and insulin calculations. The results obtained from the Single-Shot multibox Detection (SSD) MobileNet-V1 food detection

IOT-based air quality monitoring system for agriculture

Air quality assessment has been discussed for urban environments with a high degree of industrialization, as they are infested with hazardous chemicals and airborne pollutants. The assessment is carried out by monitoring stations, that basically support limited areas while leaving large geographical areas uncovered. The expansion in the agriculture sector directed us towards air quality assessment on the farms. This is because research has shown that crops can be injured when exposed to high concentrations of various air pollutants, while also affecting farmers' health states. But those air