Monte Carlo (MC) simulation is a widely adopted computational method that relies on random sampling, but it is susceptible to exhibiting patterns and biases due to the use of pseudo-random numbers. In contrast, Quasi-Monte Carlo (QMC) techniques employ low discrepancy sequences, resulting in more evenly distributed random numbers and the potential for more accurate and reliable simulation outcomes. Mushroom-Waveguide Photodetectors (WGPDs) are integrated to a wide range of applications, and their performance is critically dependent on precise dimensional parameters. In this research, we

In this paper, a highly directive meander line antenna is proposed to be utilized in the unlicensed Bluetooth band. The main goal of the proposed structure is to achieve low profile, and high gain in the Bluetooth band. Moreover, the antenna should be of low cost to be suitable for commercial use. The proposed structure is simulated using HFSS and CST to verify the obtained results. The maximum calculated gain of the antenna is 9.95 dBi (9.79 dBi) along the end-fire direction as simulated by HFSS (CST). The antenna demonstrated high radiation efficiency which is around 96% over its working

Lithium-ion batteries are crucial building stones in many applications. Therefore, modeling their behavior has become necessary in numerous fields, including heavyweight ones such as electric vehicles and plug-in hybrid electric vehicles, as well as lightweight ones like sensors and actuators. Generic models are in great demand for modeling the current change over time in real-time applications. This paper proposes seven dynamic models to simulate the behavior of lithium-ion batteries discharging. This was achieved using NASA room temperature random walk discharging datasets. The efficacy of

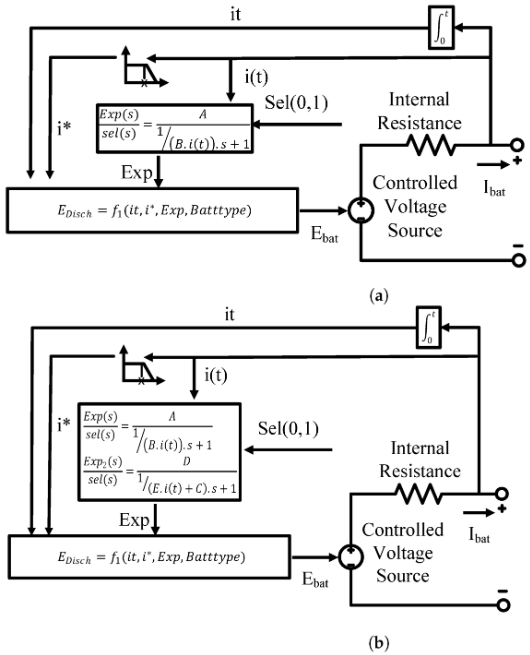

In various areas of life, rechargeable lithium-ion batteries are the technology of choice. Equivalent circuit models are utilized extensively in characterizing and modeling energy storage systems. In real-time applications, several generic-based battery models are created to simulate the battery's charging and discharging behavior more accurately. In this work, we present two generic battery models based on Mittag-Leffler function using a generic Standard battery model as a reference. These models are intended to fit the continuous discharging cycles of lithium-ion, Nickel-cadmium, and Nickel

This paper introduces an efficient prediction algorithm tailored for advanced and high efficiency video coding, encompassing both H.264 and H.265. The proposed approach aims at replacing the standard intra prediction methodology by employing a streamlined prediction mode, which significantly reduces computational overhead and system complexity while eliminating the requirement for mode decision. By leveraging block comparison criteria, the designed method combines neighboring blocks in a linear fashion to accurately represent the target block. Extensive comparisons are conducted with the H.264

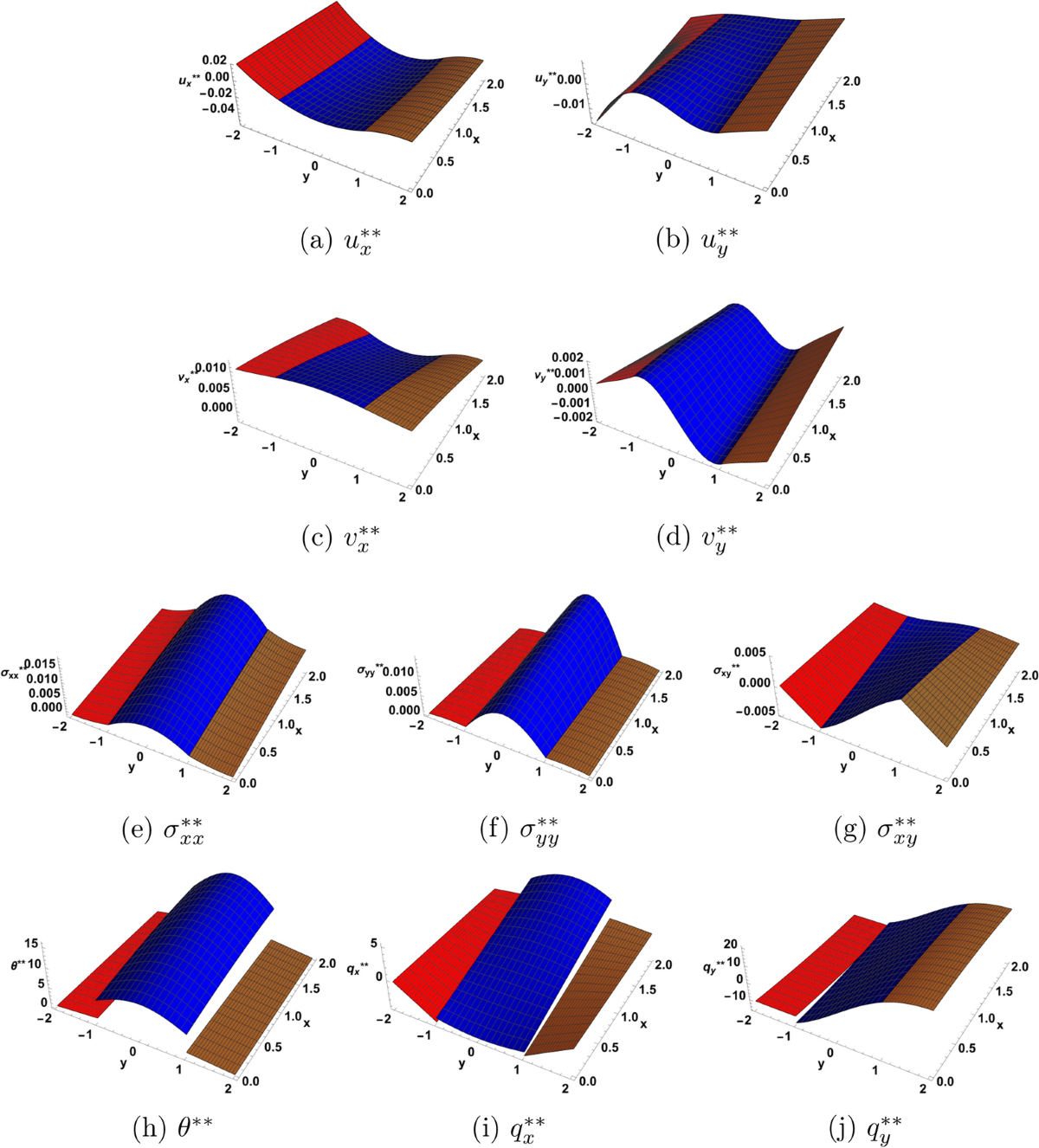

Plane, nonlinear Rayleigh wave propagation is investigated in a three-layer sandwich structure of a thermoelastic medium, within the frame of dual-phase-lag theory. The thermal conductivity is taken as a linear function of temperature. This induces nonlinearity in the evolution equations for the heat flux components. A particular solution is found in the form of Poincaré expansion in a small parameter that reflects the fluctuations of temperature about a steady value. This solution is discussed and plots are provided for a special case when both external faces of the structure are traction

We investigate a one-dimensional restriction of a nonlinear model of thermo-electroelasticity in extended thermodynamics and in the quasi-electrostatic regime (see Ghaleb et al. in Int J Eng Sci 119:29–39, 2017. https://doi.org/10.1016/j.ijengsci.2017.06.010). An additional dependence of the thermal conductivity and the thermal relaxation time on temperature and heat flux is introduced. The aim of the present work is to assess the effect of some quadratic nonlinear couplings between the mechanical, thermal and electric fields. Such couplings are known to have a crucial effect on the stability

The model of generalized thermoelasticity, with the dual-phase-lag theory (DPL), is applied to study the influence of gravity on a piezo-thermoelastic diffusive medium. Normal mode analysis is used to obtain the exact expressions for different physical quantities. The derived expressions are computed numerically and the results are presented in graphical form. Comparisons are made with the results predicted by the Lord-Shulman theory (LS) and the DPL model in the presence and absence of gravity. © 2023 World Scientific Publishing Europe Ltd.

The model of generalized thermoelasticity, dual-phase-lag model (DPL), is applied to study the influence of gravity on a piezo-thermoelastic diffusive medium. Normal mode analysis is used to obtain the expressions for different physical quantities. The derived expressions are computed numerically and the results are presented in graphical form. Comparisons are made with the results predicted by Lord–Shulman theory (L–S) and DPL model in the presence and absence of gravity. © 2022, The Author(s), under exclusive licence to Springer-Verlag GmbH Germany, part of Springer Nature.

An efficient numerical approach based on weighted-average finite differences is used to solve the Newtonian plane Couette flow with wall slip, obeying a dynamic slip law that generalizes the Navier slip law with the inclusion of a relaxation term. Slip is exhibited only along the fixed lower plate, and the motion is triggered by the motion of the upper plate. Three different cases are considered for the motion of the moving plate, i.e., constant speed, oscillating speed, and a single-period sinusoidal speed. The velocity and the volumetric flow rate are calculated in all cases and comparisons