Breadcrumb

Circuit Theory and Applications

Lung Segmentation Using ResUnet++ Powered by Variational Auto Encoder-Based Enhancement in Chest X-ray Images

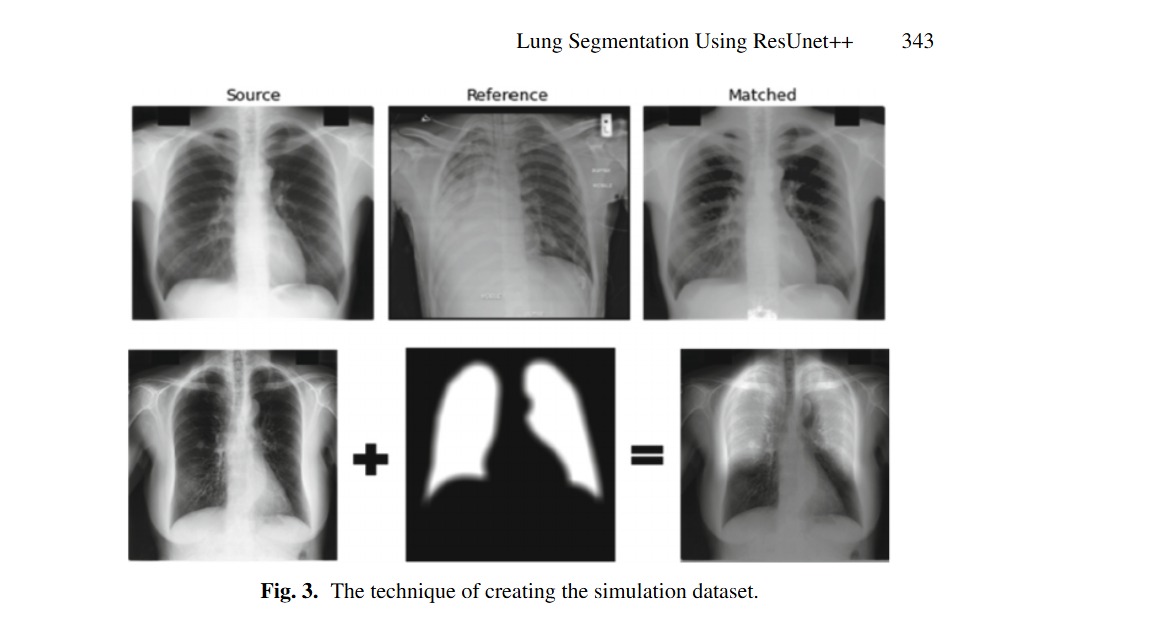

X-ray has a huge popularity around the world. This is due to its low cost and easy to access. Most of lung diseases are diagnosed using Chest X-ray (CXR). So, developing computer aided detection (CAD) provided with automatic lung segmentation can improve the efficiency of the detection and support the physicians to make a reliable decision at early stages. But when the input image has image artifacts, then any lung segmentation model will introduce suboptimal lung segmentation results. In this paper, a new approach is proposed to make the lung segmentation model robust and boost the basic

A CAD System for Lung Cancer Detection Using Chest X-ray: A Review

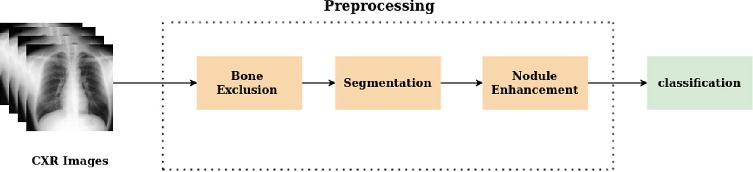

For many years, lung cancer has been ranked among the deadliest illnesses in the world. Therefore, it must be anticipated and detected at an early stage. We need to build a computer-aided diagnosis (CAD) system to help physicians to provide better treatment. In this study, the whole pipeline and the process of the CAD system for lung cancer detection in Chest X-ray are provided. It demonstrates the limitations and the problems facing lung cancer detection. New work is highlighted to be explored by the researchers in this area. Existing studies in the field are reviewed, including their

Automatic Early Diagnosis of Alzheimer's Disease Using 3D Deep Ensemble Approach

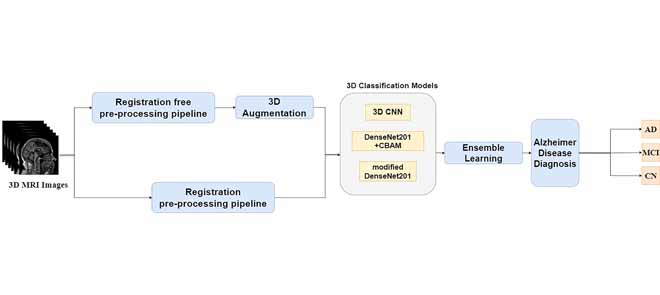

Alzheimer's disease (AD) is considered the 6 th leading cause of death worldwide. Early diagnosis of AD is not an easy task, and no preventive cures have been discovered yet. Having an accurate computer-aided system for the early detection of AD is important to help patients with AD. This study proposes a new approach for classifying disease stages. First, we worked on the MRI images and split them into an appropriate format to avoid data leakage. Subsequently, a simple and fast registration-free preprocessing pipeline was applied to the dataset. Numerous experiments were conducted to analyze

Does Deep Learning Require Image Registration for Early Prediction of Alzheimer’s Disease? A Comparative Study Using ADNI Database

Image registration is the process of using a reference image to map the input images to match the corresponding images based on certain features. It has the ability to assist the physicians in the diagnosis and following up on the patient’s condition. One of the main challenges of the registration is that it takes a huge time to be computationally efficient, accurate, and robust as it can be framed as an optimization problem. In this paper, we introduce a comparative study to investigate the influence of the registration step exclusion from the preprocessing pipeline and study the counter

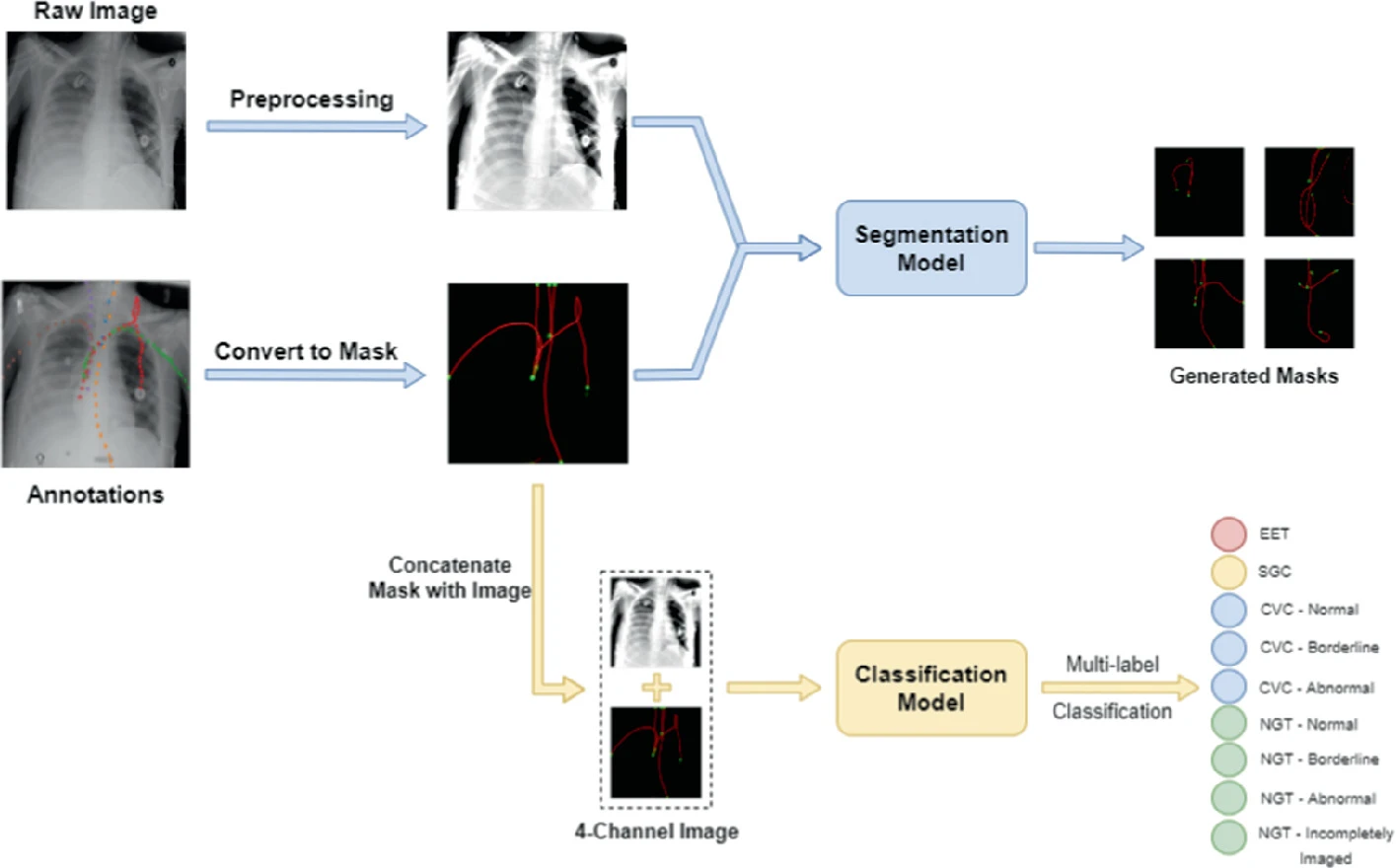

Efficient Pipeline for Rapid Detection of Catheters and Tubes in Chest Radiographs

Catheters are life support devices. Human expertise is often required for the analysis of X-rays in order to achieve the best positioning without misplacement complications. Many hospitals in underprivileged regions around the world lack the sufficient radiology expertise to frequently process X-rays for patients with catheters and tubes. This deficiency may lead to infections, thrombosis, and bleeding due to misplacement of catheters. In the last 2 decades, deep learning has provided solutions to various problems including medical imaging challenges. So instead of depending solely on

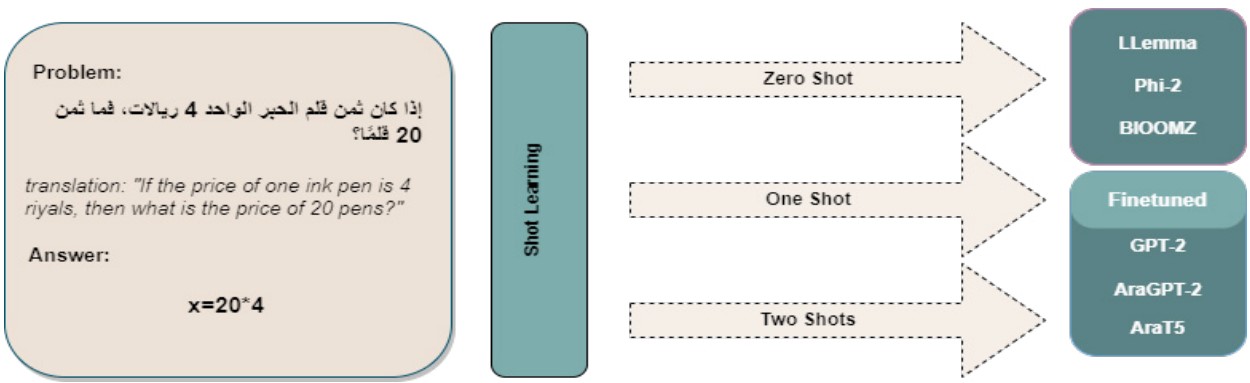

Mathematical Problem Solving in Arabic: Assessing Large Language Models

This paper comprehensively evaluates the efficacy of different large language models (LLMs) in addressing mathematical challenges expressed in natural languages, mainly focusing on low-resource languages like Arabic. The main challenge of this problem is that despite the considerable size and impressive problem-solving capabilities of these models, they still require enhancements to achieve satisfactory performance for mathematical problem-solving. An LLM must be trained or fine-tuned extensively in understanding and solving mathematical problems articulated in natural language contexts. This

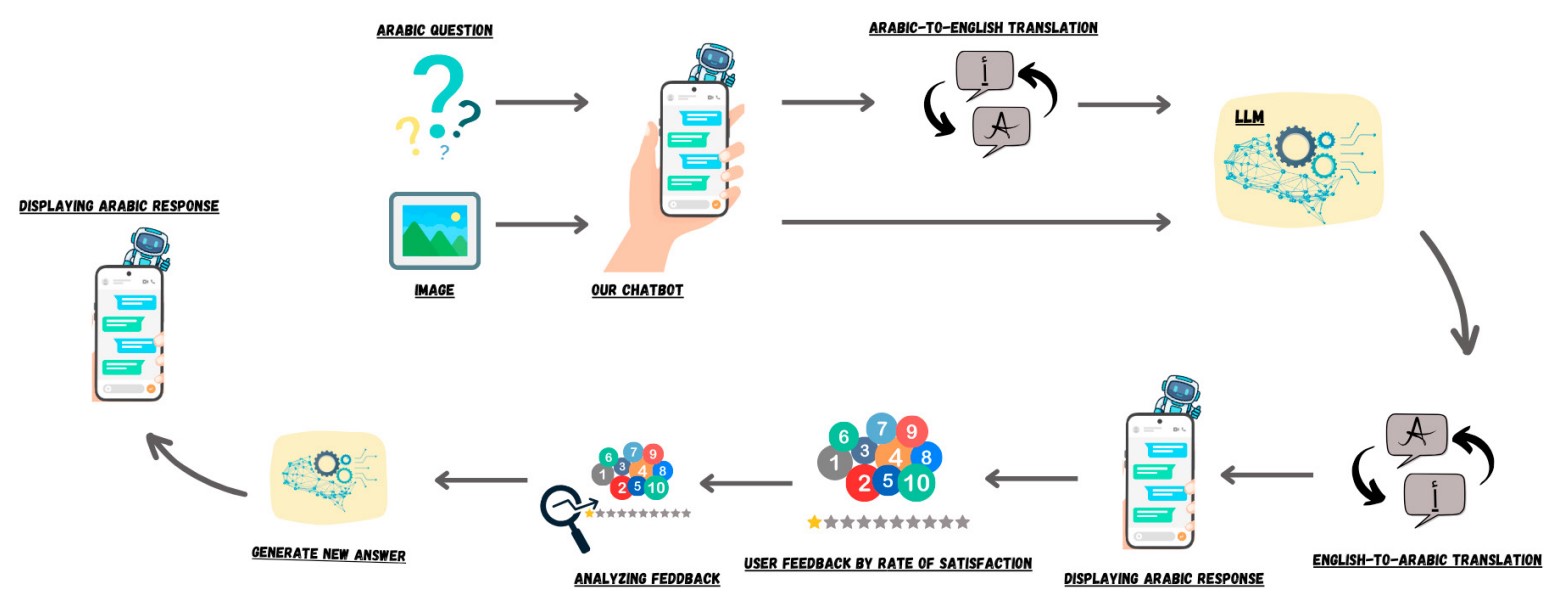

Enhancing Visual Question Answering for Arabic Language Using LLaVa and Reinforcement Learning

Visual Question Answering (VQA) systems have achieved remarkable advancements by combining text-based question answering with image analysis. This integration has resulted in the creating of machines that can comprehend and address questions related to visual content. Despite these technological developments, a notable lack of VQA solutions specifically designed for the Arabic language remains. This gap persists even with the significant progress made in deep learning techniques and the development of Large Language models (LLMs). Our research introduces ArabicQuest, an innovative chatbot

Smart Prediction of Circulatory Failure: Machine Learning for Early Detection of Patient Deterioration

Circulatory failure, also known as shock, is a critical condition that can have serious consequences for one's health. Early detection and timely intervention are crucial for improving patient outcomes. Machine learning (ML) models have shown promise in predicting circulatory failure based on clinical data. In our study, we examined different machine learning (ML) models to predict circulatory failure in patients who were admitted to the intensive care unit (ICU) with suspected circulatory problems. The ML model we developed used various algorithms like random forest, LG, XGB, Decision Tree

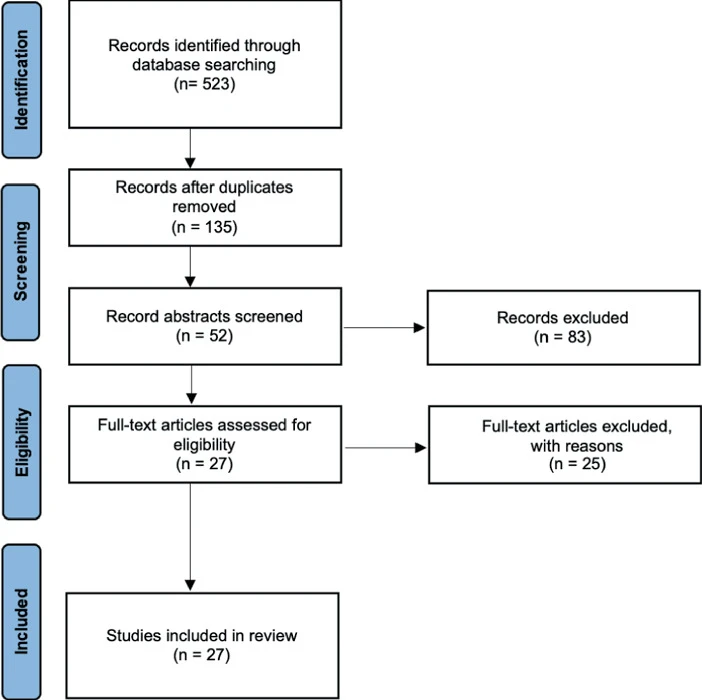

Oral Dental Diagnosis Using Deep Learning Techniques: A Review

The purpose of this study is to investigate the gradual incorporation of deep learning in the dental healthcare system, offering an easy and efficient diagnosis. For that, an electronic search was conducted in the Institute of Electrical and Electronics Engineers (IEEE) Xplore, ScienceDirect, Journal of Dentistry, Health Informatics Journal, and other credible resources. The studies varied with their tools and techniques used for the diagnosis while coping with the rapid deep-learning evolving base, with different types of conducting tools and analysis for the data. An inclusion criterion was

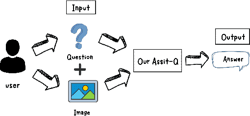

ArabicQuest: Enhancing Arabic Visual Question Answering with LLM Fine-Tuning

In an attempt to bridge the semantic gap between language understanding and visuals, Visual Question Answering (VQA) offers a challenging intersection of computer vision and natural language processing. Large Language Models (LLMs) have shown remarkable ability in natural language understanding; however, their use in VQA, particularly for Arabic, is still largely unexplored. This study aims to bridge this gap by examining how well LLMs can improve VQA models. We use state-of-the-art AI algorithms on datasets from multiple fields, including electric devices, Visual Genome, RSVQA, and ChartsQA