Breadcrumb

Circuit Theory and Applications

Synergism between Saccharomyces cerevisiae probiotic and rosemary nano-emulsion: Effect on broiler chicken meat quality and shelf life

Although several studies have investigated the effect of either probiotic feed additives or postmortem meat treatment on the quality of obtained chicken meat, the impact of combined treatment with probiotic feed additives along with meat dipping in essential oil nano-emulsion on meat shelf-life is barely examined. There-fore, this study investigated the effect of combined treatment with Saccharomyces cerevisiae yeast (SCY) and rosemary oil nano-emulsion (RNE) on the quality and shelf-life of chilled broiler meat. The experimental part consisted of adding SCY as a feed additive to broiler

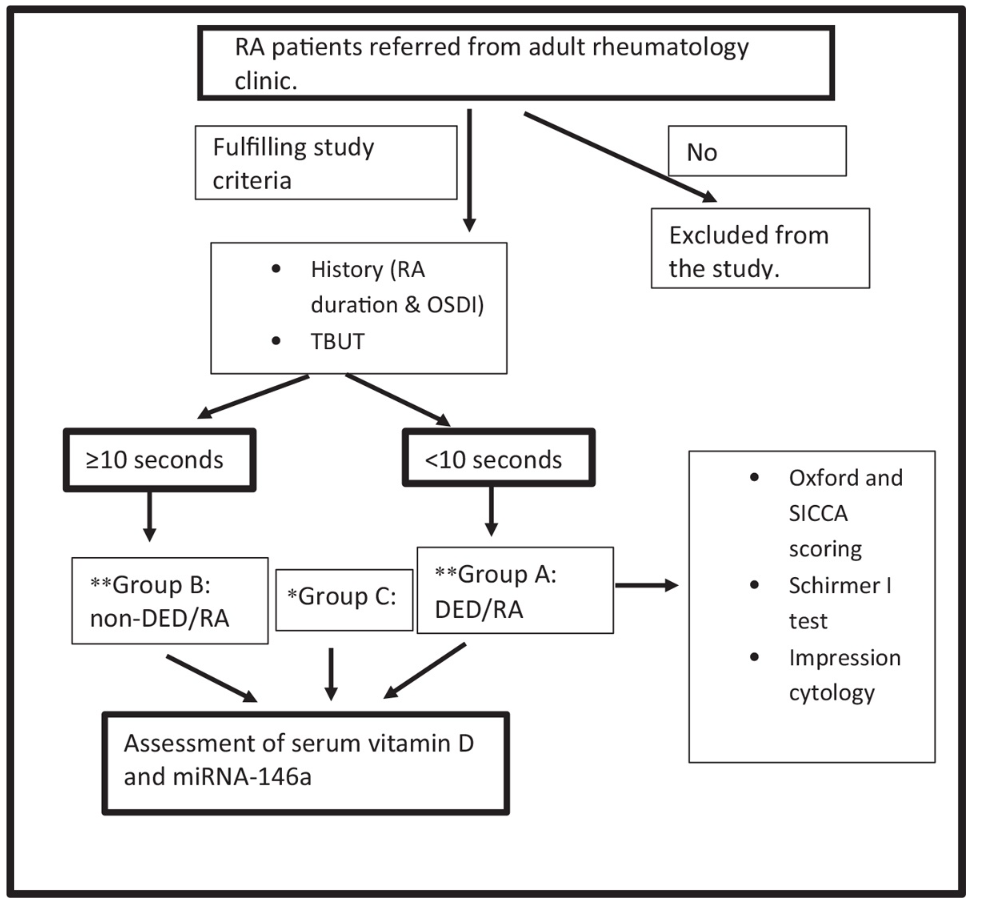

Serum vitamin D level and micro-ribonucleic acid-146a expression pattern in dry eye disease associated with rheumatoid arthritis in an Egyptian population

Aim The aim of this research was to study serum vitamin D and micro-ribonucleic acid-146a (miRNA-146a) expression in dry eye disease (DED) associated with rheumatoid arthritis (RA) and their clinical correlations to DED parameters. Setting and design This is an observational cross-sectional study that was conducted at Cairo University, Cairo, Egypt. Patients and methods The study participants were divided into three groups: group A, DED/RA (n=35); group B, non-DED/RA (n=36); and group C, non-DED/non-RA (n=35). All participants were assessed for ocular surface disease index, tear breakup time

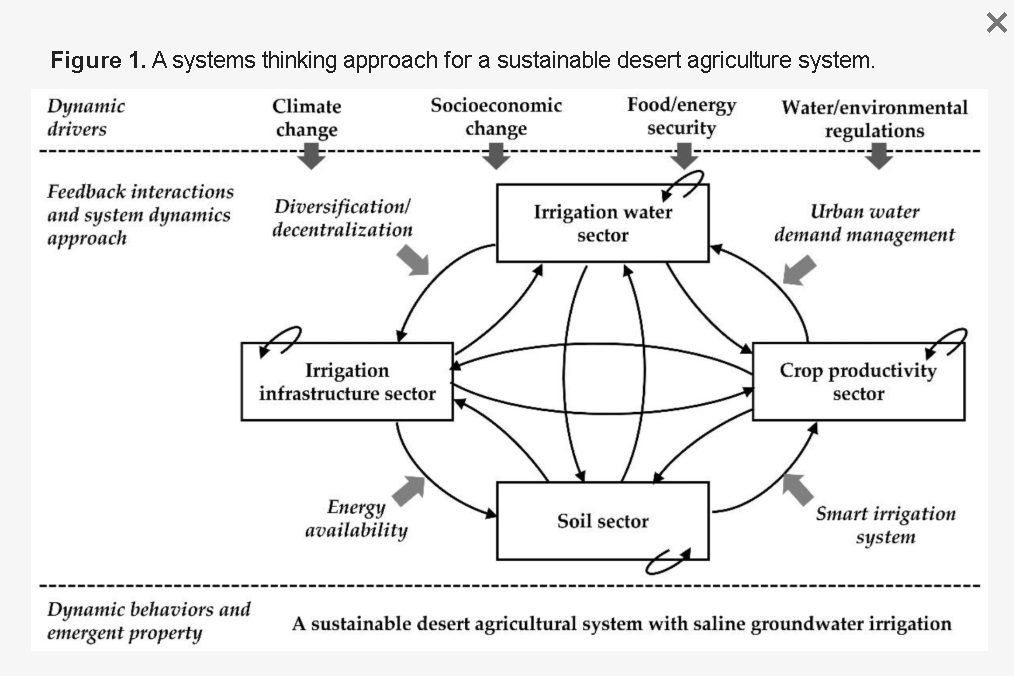

Systems Thinking for Planning Sustainable Desert Agriculture Systems with Saline Groundwater Irrigation: A Review

Agricultural land expansion is a solution to address global food security challenges in the context of climate change. However, the sustainability of expansion in arid countries is difficult because of scarce surface water resources, groundwater salinity, and the health of salt-affected soil. Developing expansion and sustainability plans for agriculture requires systems thinking, considering the complex feedback interactions between saline groundwater, salt-affected soil, plant growth, freshwater mixing with saline groundwater, irrigation systems, and the application of soil amendments to

Gamma radiation reduces the levels of aflatoxins B1 in poultry meat, skin, and liver

Aflatoxins are one of the most dangerous toxic residues in various foods including poultry. This study was conducted to assess the reducing effect of gamma radiation on the levels of aflatoxin B1 in poultry meat, skin, and liver. To this end, a total of 80 poultry samples including meat, skin, and liver were surveyed for the incidence of aflatoxins, where only positive samples (27 samples of muscle, skin, and liver; 9 samples each) were selected for testing the effect of treatment by gamma radiation. The levels of aflatoxins were estimated in the examined samples using High Performance Liquid

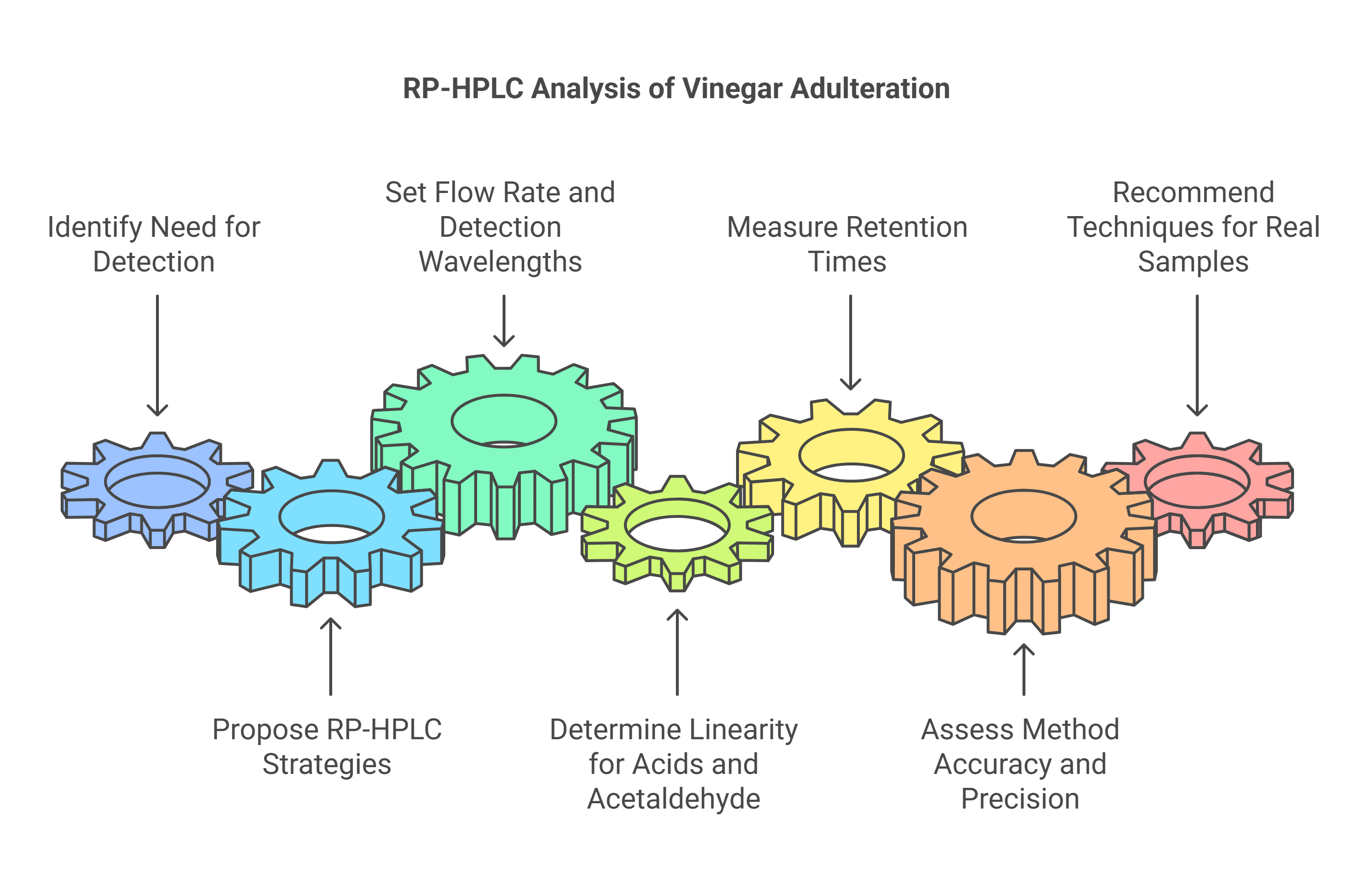

Detection and Identification of Adulteration in Vinegar Samples Based on Reversed-Phase High-Performance Liquid Chromatographic (RP-HPLC) Strategies

Adulteration of vinegar to gain economic benefit has become a common practice in recent years. RP-HPLC strategies were proposed for the assurance of the concentration of acetic acid, rare organic acids (tartaric, malic, lactic and citric), and acetaldehyde in Egyptian vinegar samples. The flow rate was 0.5 mL/min using UV detection at 210 and 365 nm for organic acid and acetaldehyde, respectively. The linearity was 0.05-0.60 g/100 mL for acetic acid, 0.01-0.12 g/100 mL for citric, malic, and tartaric acids, 0.005-0.060 g/100 mL for lactic acid, and 0.02-0.16 mg/L for acetaldehyde with r2 > 0

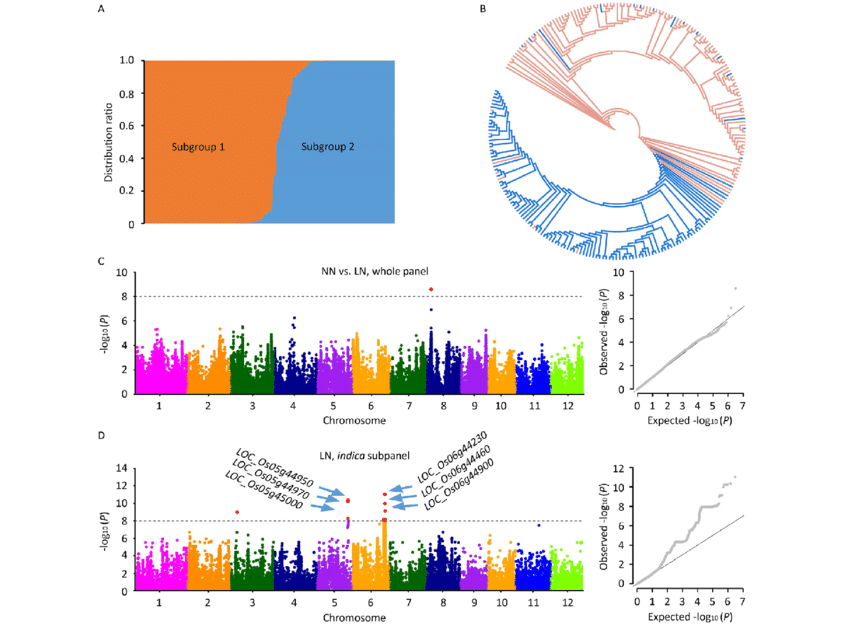

Identification of Candidate Genes for Rice Nitrogen Use Efficiency by Genome-wide Association Analysis; [全基因组关联分析(GWAS)鉴定水稻氮素利用效率候选基因]

【Objective】 The exploration of germplasm and gene resources in rice for high nitrogen efficiency, along with the elucidation of their molecular mechanisms and genetic effects, represents a significant focus and goal within current research efforts on rice nitrogen use efficiency (NUE).【Method】 To identify the variant loci and candidate genes associated with rice NUE, we collected 190 Asian rice accessions as an association population. After thorough filtering and screening, we obtained 3, 934, 195 high-quality single nucleotide polymorphisms (SNPs). Under field conditions, two nitrogen

Correction to: Identification of TIMPs signatures in Randall plaque from single-cell RNA sequencing (scRNA-Seq) analysis (Functional & Integrative Genomics, (2024), 24, 1, (11), 10.1007/s10142-024-01296-0)

The original article contains an error. Abstract has been removed during processing. This is now added here. Background Tissue inhibitors of metalloproteinases (TIMPs) are essential for controlling the dynamics of the extracellular matrix. Although their role in vascular diseases like as atherosclerosis and plaque development has been widely researched, the specific patterns of their expression and their functional significance inside Randall plaque tissues, a distinct vascular pathology linked to nephrolithiasis, have not been well investigated. Objectives The objective of this work was to

Comparative genomics and proteomics analysis on Capsicum species reveals insights about the capsaicin biosynthesis

Capsaicin is the primary capsaicinoid compound responsible for the spiciness of chilli peppers. Several known and unknown genes synthesize capsaicin through various metabolic pathways, such as the phenylpropanoid or the L-valine metabolism pathways. We conducted comprehensive comparative genomics and proteomics analyses to identify genes and proteins associated with the capsaicin pathway in Capsicum chinense, Capsicum baccatum and the two C.annuum cultivars, CM334 and ECW. A BLAST search against the NCBI database identified 26 and 58 enzyme genes and proteins, respectively. These enzyme genes

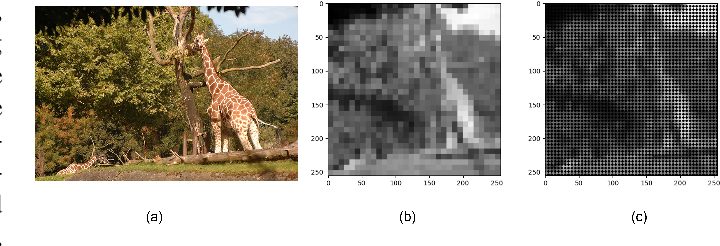

Enhancing Scene Simplification and Optimization for Retinal Prosthesis Platform

Retinal prostheses are designed to aid individuals with retinal degenerative conditions such as Retinitis Pigmentosa (RP) and Age-related Macular Degeneration (AMD). These prostheses seek to restore vision and improve the perceived scene by stimulating degenerated retinal cells using retinal stimulating electrodes. While these electrodes allow more efficient interaction with the surroundings, they offer limited resolution.This paper presents an innovative approach to revolutionize the visual perception of retinal prosthesis users. The key idea behind the proposed approach is to fuse

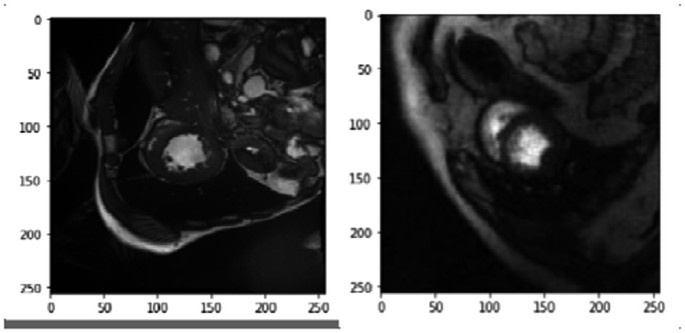

Transfer Learning in Segmenting Myocardium Perfusion Images

Cardiac magnetic resonance perfusion (CMRP) images are used to assess the local function and permeability of the heart muscle. The perfusion analysis requires the segmentation of cardiac inner and outer walls of the left ventricle (LV). However, the available perfusion datasets are limited or have no annotations. A fair dataset was annotated to employ the latest and most effective Deep Learning (DL) methodologies. In this paper, we employ similar cardiac imaging protocols in terms of cardiac geometry by initially training using CINE images and performing domain adaptation to CMRP images using