Breadcrumb

Circuit Theory and Applications

Deep Neural Networks-Based Weight Approximation and Computation Reuse for 2-D Image Classification

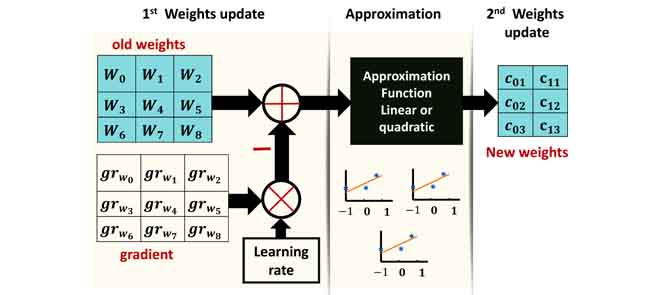

Deep Neural Networks (DNNs) are computationally and memory intensive, which present a big challenge for hardware, especially for resource-constrained devices such as Internet-of-Things (IoT) nodes. This paper introduces a new method to improve DNNs performance by fusing approximate computing with data reuse techniques for image recognition applications. First, starting from the pre-Trained network, then the DNNs weights are approximated based on the linear and quadratic approximation methods during the retraining phase to reduce the DNN model size and number of arithmetic operations. Then, the

DT2CAM: A Decision Tree to Content Addressable Memory Framework

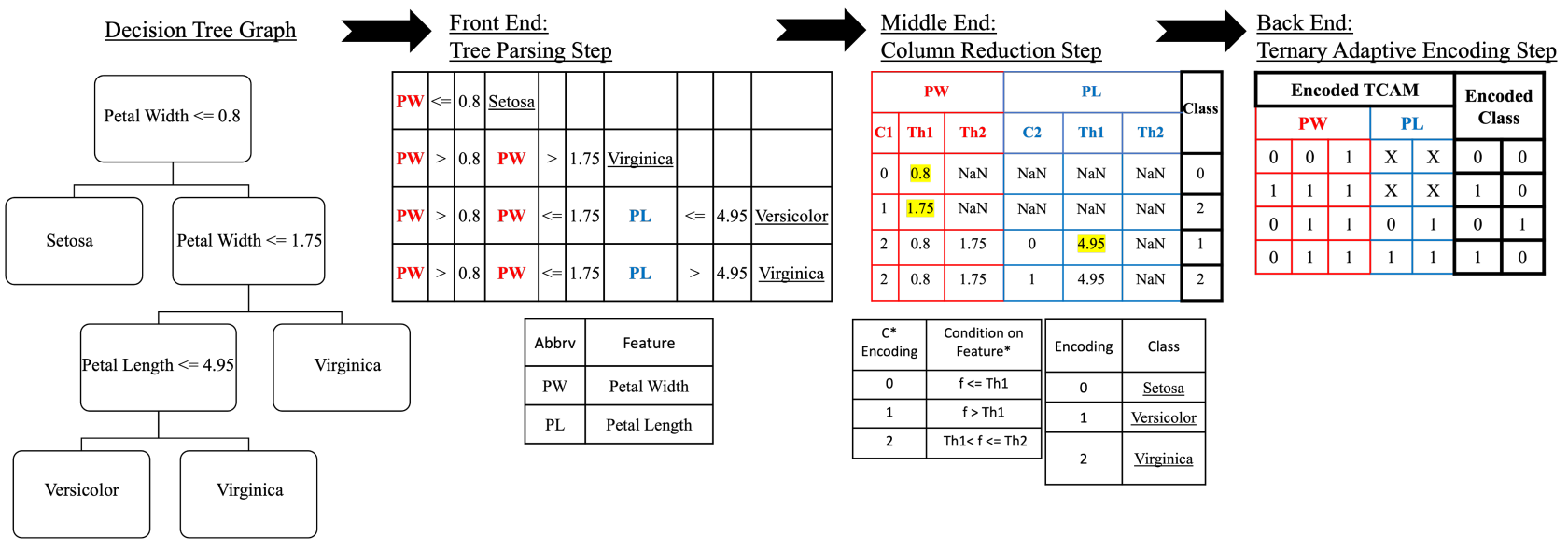

Decision trees are powerful tools for data classification. Accelerating the decision tree search is crucial for on-the-edge applications with limited power and latency budget. In this article, we propose a content-addressable memory compiler for decision tree inference acceleration. We propose a novel 'adaptive-precision' scheme that results in a compact implementation and enables an efficient bijective mapping to ternary content addressable memories while maintaining high inference accuracies. We also develop a resistive-based functional synthesizer to map the decision tree to resistive

Design of Complex-Order PI/PID Speed Controllers and its FPAA Realization

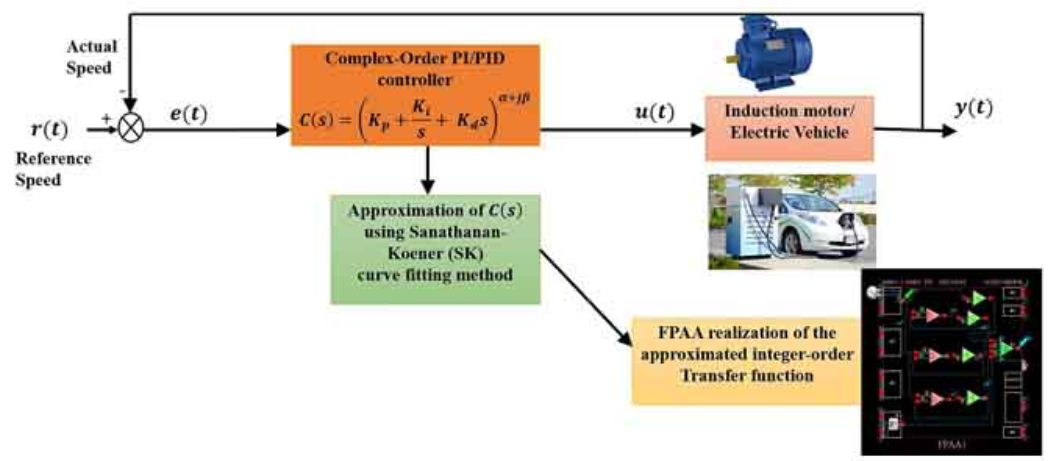

Complex-order controllers are a generalized version of conventional integer-order controllers and are known to offer greater flexibility, better robustness, and improved system performance. This paper discusses the design of complex-order PI/PID controllers to control the speed of an induction motor drive and an electric vehicle. The speed-tracking performance of the complex-order controllers is compared with fractional-order controllers and conventional integer-order controllers. Implementing complex-order controllers is challenging due to commercial complex-order fractance element

A note on the bandwidth of negative group delay filters

An updated definition of group delay bandwidth in analog filters is introduced in this work. Unlike existing definitions, this new definition considers simultaneously the value of the group delay and filter gain, leading to minimized distortion in the filter output. In addition, it offers the capability of handling wide-band signals without introducing errors in the shape of their envelopes. Selected first- and second-order filters are studied and simulation results are provided to validate the efficiency of the new definition. © 2024 The Author(s). International Journal of Circuit Theory and

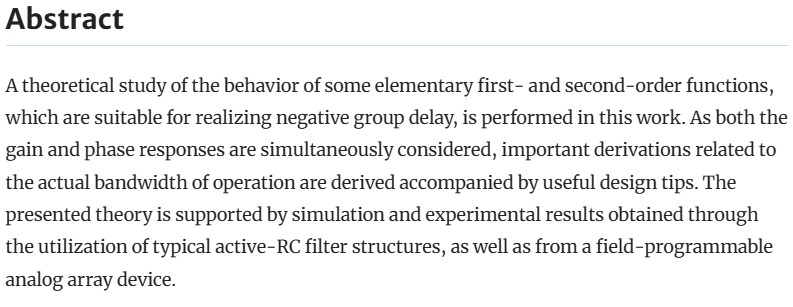

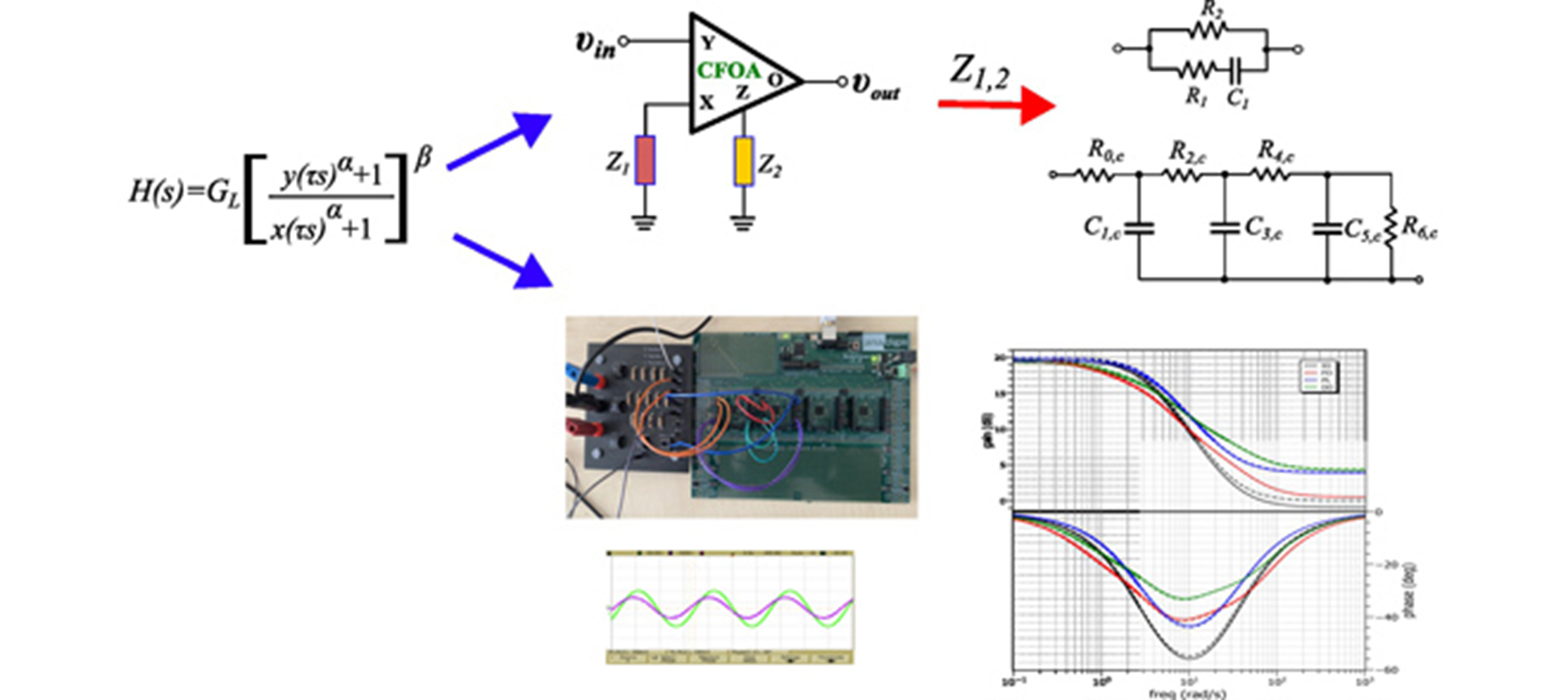

Elementary Negative Group Delay Filter Functions

A theoretical study of the behavior of some elementary first- and second-order functions, which are suitable for realizing negative group delay, is performed in this work. As both the gain and phase responses are simultaneously considered, important derivations related to the actual bandwidth of operation are derived accompanied by useful design tips. The presented theory is supported by simulation and experimental results obtained through the utilization of typical active-RC filter structures, as well as from a field-programmable analog array device. © The Author(s) 2024.

Bilinear Double-Order Filter Designs and Application Examples

A novel kind of non-integer order bilinear filters, named double-order bilinear filters, is introduced in this work. They are based on the employment of two non-integer orders, offering the maximum design flexibility in comparison with their fractional-order and power-law counterparts. An attractive offered benefit is that this is achieved without increasing the circuit complexity, since the proposed structure is capable of realizing all non-integer kinds of filters. Two design examples are provided, where it is shown that lead/lag compensators utilized in control applications and low/high

Minimum Active Component Count Design of a PIλDμ Controller and Its Application in a Cardiac Pacemaker System †

A generalized structure for implementing fractional-order controllers is introduced in this paper. This is achieved thanks to the consideration of the controller transfer function as a ratio of integer and non-integer impedances. The non-integer order impedance is implemented using RC networks, such as the Foster and Cauer networks. The main offered benefit, with regards to the corresponding convectional implementations, is the reduced active and, also, passive component count. To demonstrate the versatility of the proposed concept, a controller suitable for implementing a cardiac pacemaker

Retraction Note: Hybrid rough-bijective soft set classification system (Neural Computing and Applications, (2018), 29, 8, (67-78), 10.1007/s00521-016-2711-z)

Retraction to: Neural Comput & Applic (2018) 29:67–78https://doi.org/10.1007/s00521-016-2711-z. The Editor-in-Chief and the publisher have retracted this article. The article was submitted to be part of a guest-edited issue. An investigation by the publisher found a number of articles, including this one, with a number of concerns, including but not limited to compromised editorial handling and peer review process, inappropriate or irrelevant references or not being in scope of the journal or guest-edited issue. Based on the investigation’s findings the Editor-in-Chief therefore no longer has

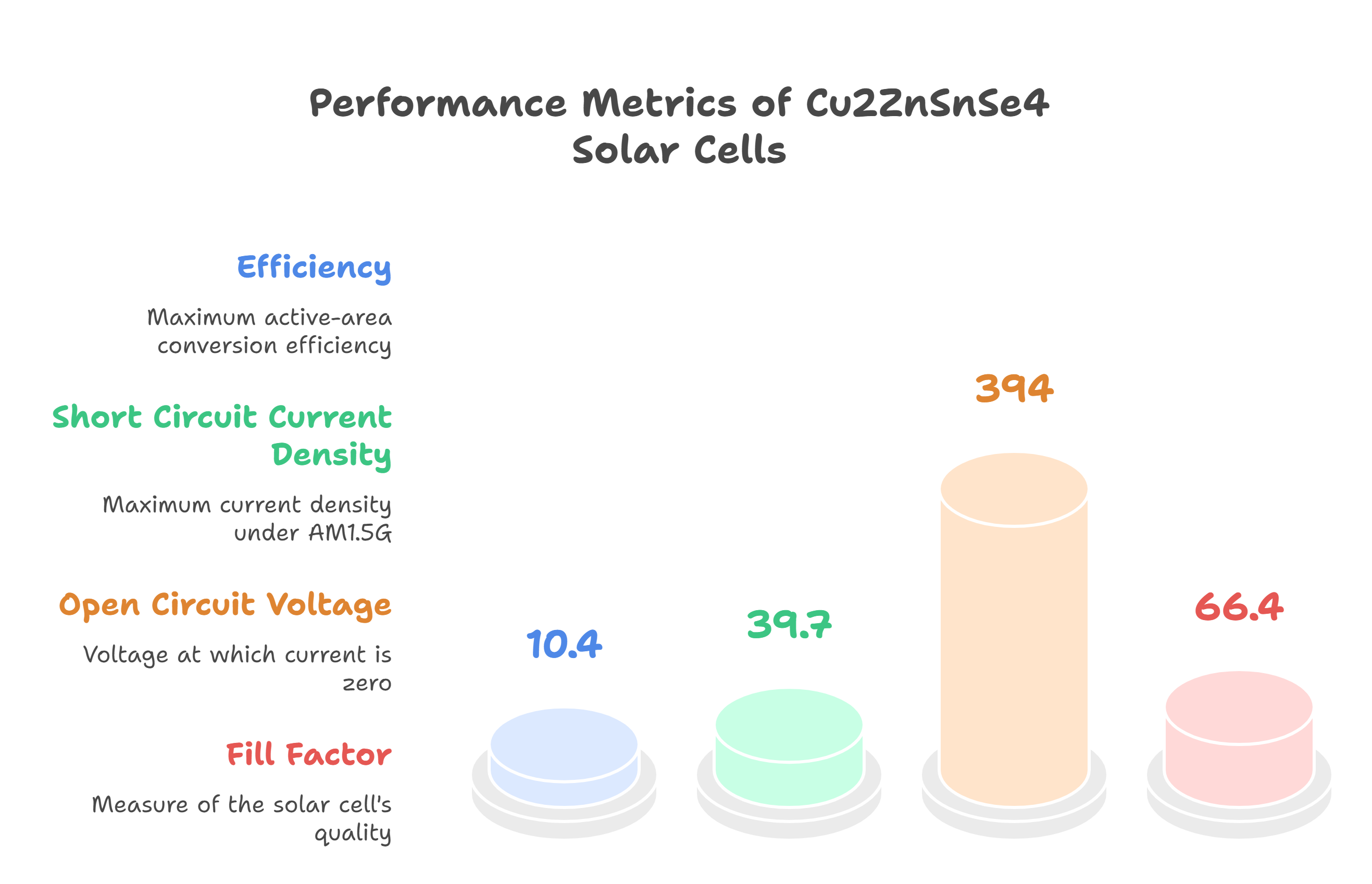

Physical and electrical characterization of high-performance Cu2ZnSnSe4based thin film solar cells

We report on the electrical, optical and physical properties of Cu2ZnSnSe4solar cells using an absorber layer fabricated by selenization of sputtered Cu, Zn and Cu10Sn90multilayers. A maximum active-area conversion efficiency of 10.4% under AM1.5G was measured with a maximum short circuit current density of 39.7 mA/cm2, an open circuit voltage of 394 mV and a fill factor of 66.4%. We perform electrical and optical characterization using photoluminescence spectroscopy, external quantum efficiency, current-voltage and admittance versus temperature measurements in order to derive information

Reduce Computing Complexity of Deep Neural Networks Through Weight Scaling

Large deep neural network (DNN) models are computation and memory intensive, which limits their deployment especially on edge devices. Therefore, pruning, quantization, data sparsity and data reuse have been applied to DNNs to reduce memory and computation complexity at the expense of some accuracy loss. The reduction in the bit-precision results in loss of information, and the aggressive bit-width reduction could result in noticeable accuracy loss. This paper introduces Scaling-Weight-based Convolution (SWC) technique to reduce the DNN model size and the complexity and number of arithmetic