Breadcrumb

Circuit Theory and Applications

Deep learning models for predicting RNA degradation via dual crowdsourcing

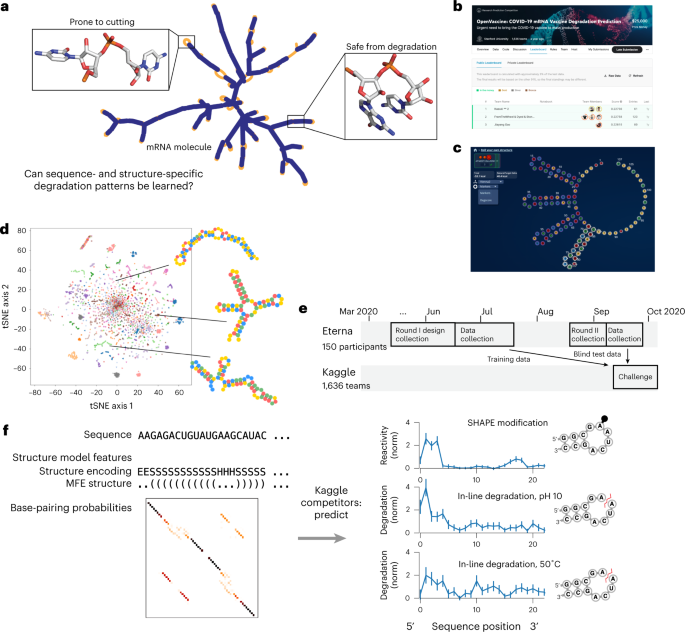

Medicines based on messenger RNA (mRNA) hold immense potential, as evidenced by their rapid deployment as COVID-19 vaccines. However, worldwide distribution of mRNA molecules has been limited by their thermostability, which is fundamentally limited by the intrinsic instability of RNA molecules to a chemical degradation reaction called in-line hydrolysis. Predicting the degradation of an RNA molecule is a key task in designing more stable RNA-based therapeutics. Here, we describe a crowdsourced machine learning competition (‘Stanford OpenVaccine’) on Kaggle, involving single-nucleotide

NileTMRG at SemEval-2017 Task 4: Arabic Sentiment Analysis

This paper describes two systems that were used by the NileTMRG for addressing Arabic Sentiment Analysis as part of SemEval-2017, task 4. NileTMRG participated in three Arabic related subtasks which are: Subtask A (Message Polarity Classification), Subtask B (Topic-Based Message Polarity classification) and Subtask D (Tweet quantification). For sub-task A, we made use of our previously developed sentiment analyzer which we augmented with a scored lexicon. For subtasks B and D, we used an ensemble of three different classifiers. The first classifier was a convolutional neural network for which

Bilingual Embeddings andWord Alignments for Translation Quality Estimation

This paper describes our submission UFAL MULTIVEC to the WMT16 Quality Estimation Shared Task, for English- German sentence-level post-editing effort prediction and ranking. Our approach exploits the power of bilingual distributed representations, word alignments and also manual post-edits to boost the performance of the baseline QuEst++ set of features. Our model outperforms the baseline, as well as the winning system in WMT15, Referential Translation Machines (RTM), in both scoring and ranking sub-tasks. © 2016 Association for Computational Linguistics.

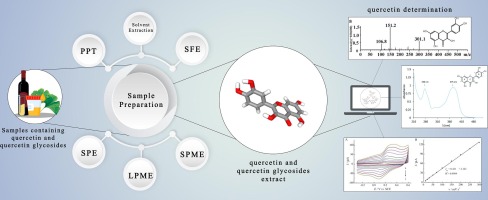

Sample preparation methods for determination of quercetin and quercetin glycosides in diverse matrices

Quercetin and its glycosides have gained a lot of interest due to their potential applications in preventing and treating various diseases. Quercetin is naturally available in free and glycoside forms such as isoquercitrin, rutin, avicularin, hyperoside, quercitrin, and others. These glycosides are more soluble and hence more bioavailable than quercetin. Determining the amount of quercetin in plants and foods is crucial to assess the quality of its natural sources, because the quercetin content changes with the species, variety, and the cultivation season. Furthermore, the concentrations of

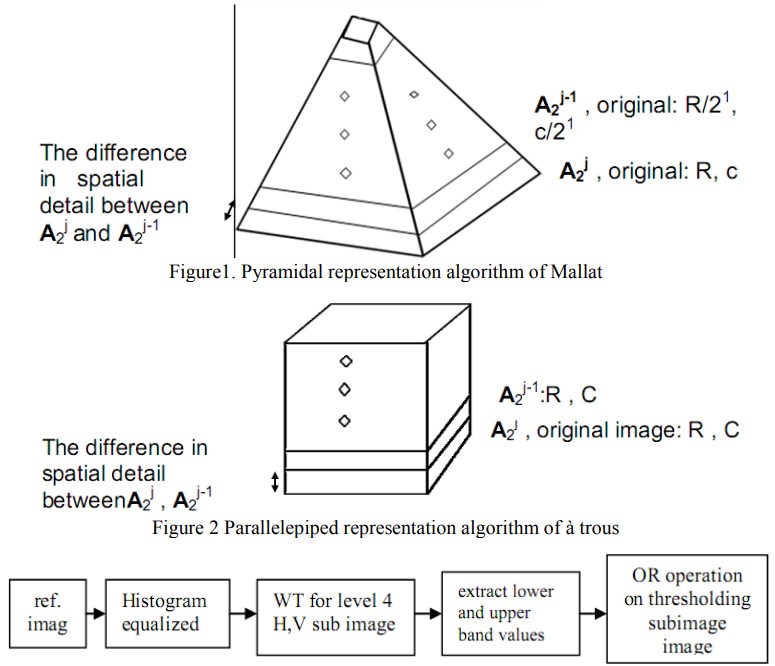

Fully Automated Fabric Defect Detection Using Additive Wavelet Transform

This paper introduces a proposed fabric defect detection technique based on additive wavelet transform. In this paper, à trous wavelet is utilized to extract the approximate sub image at an appropriate level. The objective of the proposed technique is to enhance energy of defective region and attenuate energy of background in the selected level. An improved thresholding method based on statistical calculation is used. © 2020, Menoufia University, Faculty of Electronic Engineering. All rights reserved.

Innovative approaches to metabolic dysfunction-associated steatohepatitis diagnosis and stratification

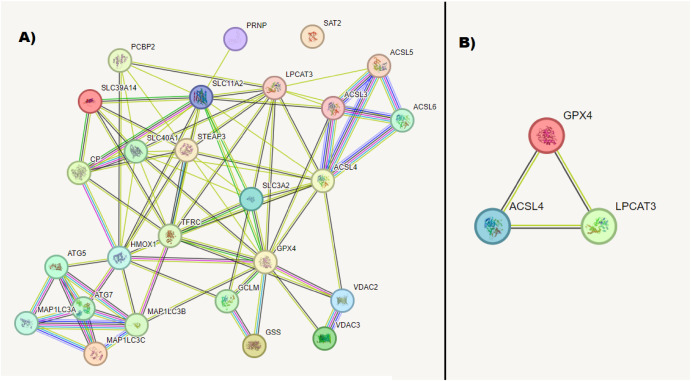

The global rise in Metabolic dysfunction-associated steatotic liver disease (MASLD)/Metabolic dysfunction-associated steatohepatitis (MASH) highlights the urgent necessity for noninvasive biomarkers to detect these conditions early. To address this, we endeavored to construct a diagnostic model for MASLD/MASH using a combination of bioinformatics, molecular/biochemical data, and machine learning techniques. Initially, bioinformatics analysis was employed to identify RNA molecules associated with MASLD/MASH pathogenesis and enriched in ferroptosis and exophagy. This analysis unveiled specific

Vehicle to Pedestrian Systems: Survey, Challenges and Recent Trends

The accelerated rise of new technologies has reshaped the manufacturing industry of contemporary vehicles. Numerous technologies and applications have completely revolutionized the driving experience in terms of both safety and convenience. Although vehicles are now connected and equipped with a multitude of sensors and radars for collision avoidance, millions of people suffer serious accidents on the road, and unfortunately, the death rate is still on the rise. Collisions are still a dire reality for vehicles and pedestrians alike, which is why the improvement of collision prevention

Identifying Immunological and Clinical Predictors of COVID-19 Severity and Sequelae by Mathematical Modeling

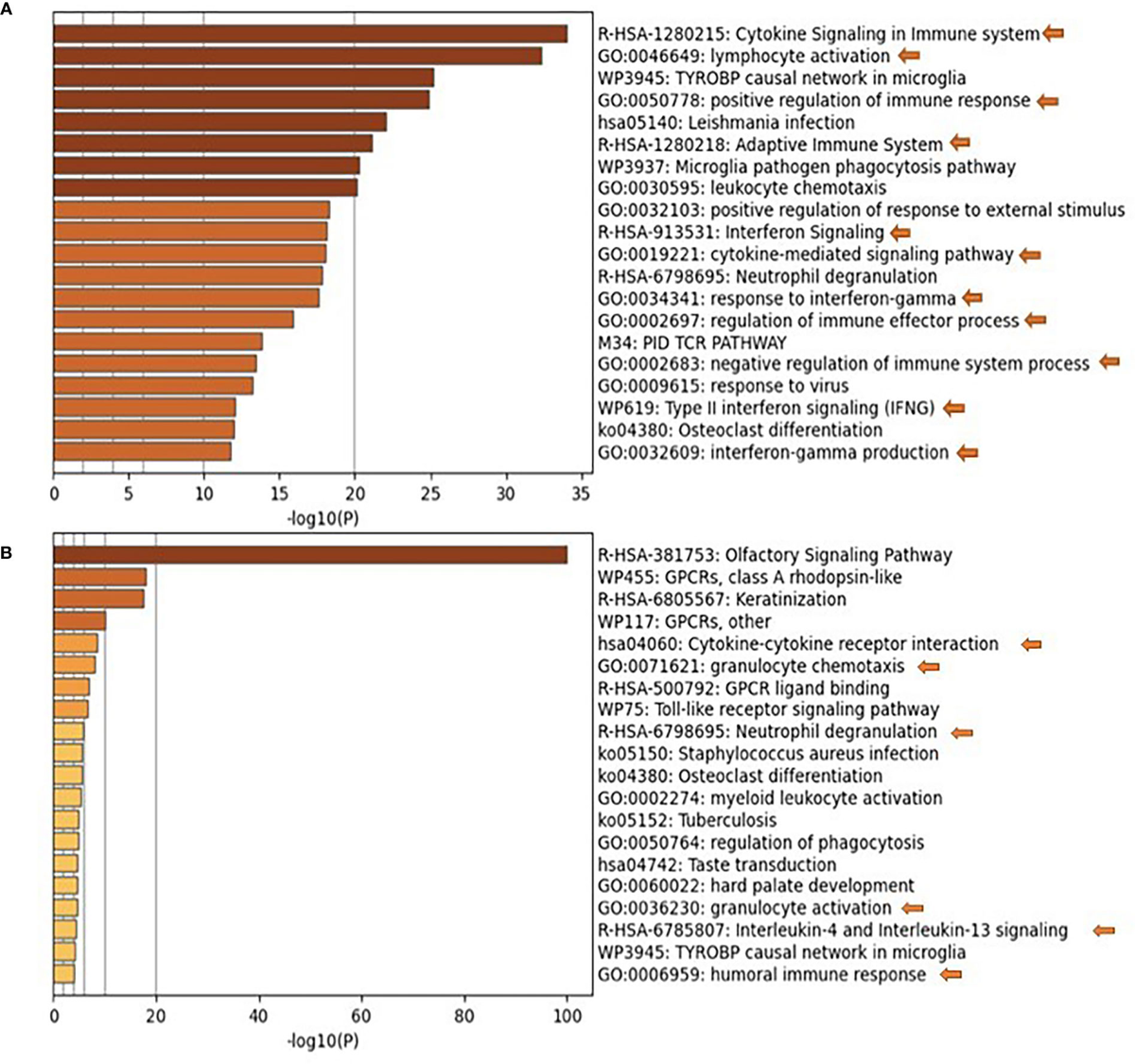

Since its emergence as a pandemic in March 2020, coronavirus disease (COVID-19) outcome has been explored via several predictive models, using specific clinical or biochemical parameters. In the current study, we developed an integrative non-linear predictive model of COVID-19 outcome, using clinical, biochemical, immunological, and radiological data of patients with different disease severities. Initially, the immunological signature of the disease was investigated through transcriptomics analysis of nasopharyngeal swab samples of patients with different COVID-19 severity versus control

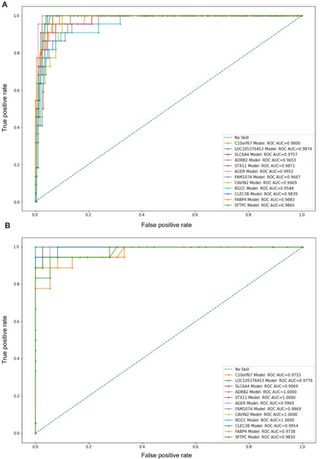

A feature selection-based framework to identify biomarkers for cancer diagnosis: A focus on lung adenocarcinoma

Lung cancer (LC) represents most of the cancer incidences in the world. There are many types of LC, but Lung Adenocarcinoma (LUAD) is the most common type. Although RNA-seq and microarray data provide a vast amount of gene expression data, most of the genes are insignificant to clinical diagnosis. Feature selection (FS) techniques overcome the high dimensionality and sparsity issues of the large-scale data. We propose a framework that applies an ensemble of feature selection techniques to identify genes highly correlated to LUAD. Utilizing LUAD RNA-seq data from the Cancer Genome Atlas (TCGA)

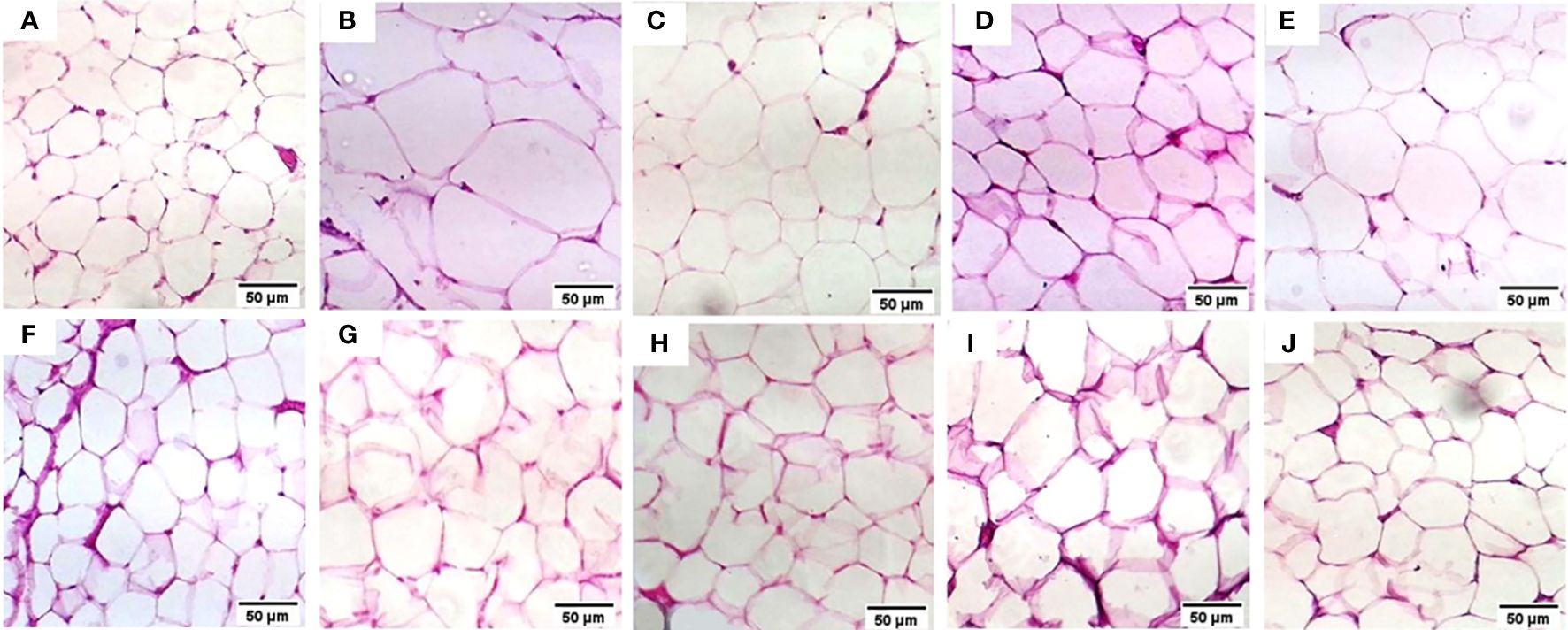

Comprehensive machine learning models for predicting therapeutic targets in type 2 diabetes utilizing molecular and biochemical features in rats

Introduction: With the increasing prevalence of type 2 diabetes mellitus (T2DM), there is an urgent need to discover effective therapeutic targets for this complex condition. Coding and non-coding RNAs, with traditional biochemical parameters, have shown promise as viable targets for therapy. Machine learning (ML) techniques have emerged as powerful tools for predicting drug responses. Method: In this study, we developed an ML-based model to identify the most influential features for drug response in the treatment of type 2 diabetes using three medicinal plant-based drugs (Rosavin, Caffeic