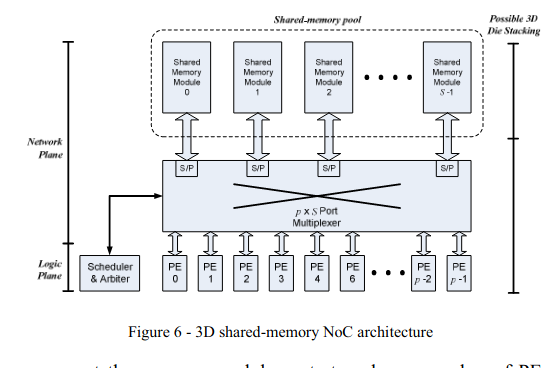

Novel 3D memory-centric NoC architecture for transaction-based SoC applications

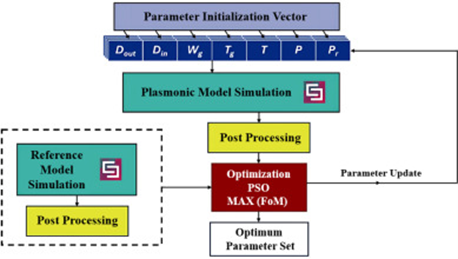

Large and complex system-on-chip devices consisting of many processor cores, accelerators, DSP functions and many other processing and memory elements are becoming common in the semiconductor industry nowadays. To communicate, these processing and memory elements need to have a network-on-chip (NoC) that is scalable enough to support large number of elements and large bandwidth among other requirements. This paper evaluates the performance of the 2D memory-centric NoC architecture from throughput and latency perspective versus the Mesh topology. We also propose a memory-centric architecture that takes advantage of developments in 3D integration technologies. The advantages of 3D memory-centric NoCs from physical design, performance and manufacturing points of view are discussed. The proposed architecture is based on a shared-memory pool that is suitable for transaction-based applications. Also, as the crossbar is a critical component in the memory-shared NoC, special 3D crossbar architecture has been proposed. © 2011 IEEE.