Single-Transistor Second-Order Allpass Filters

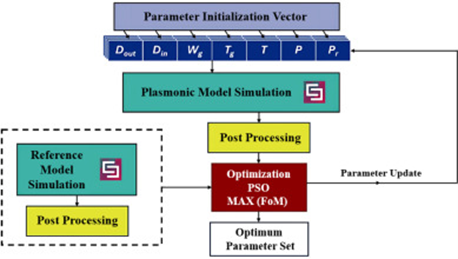

This paper presents two CMOS designs of a second-order voltage-mode allpass filters (APFs) for high-frequency applications. Each of the proposed filters is based only on a single transistor and four surrounding impedances. The first proposed allpass filter is an RL filter while the second proposed one is an RLC filter. A detailed analysis along with the parasitic effects is provided for each of the proposed filters. As a proof of concept, one design was constructed and verified experimentally using discrete MOS transistors at a 2.3MHz pole frequency. The experimental results showed a group delay of approximately 165ns with a quality factor of 1. The second design was simulated in 65-nm CMOS process and demonstrated a group delay of 22ps within a bandwidth of 18GHz with total power consumption of 9mW. © 2019 IEEE.