Permutation-Only FPGA Realization of Real-Time Speech Encryption

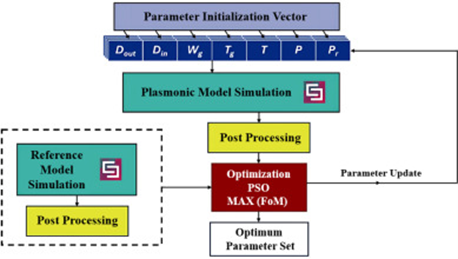

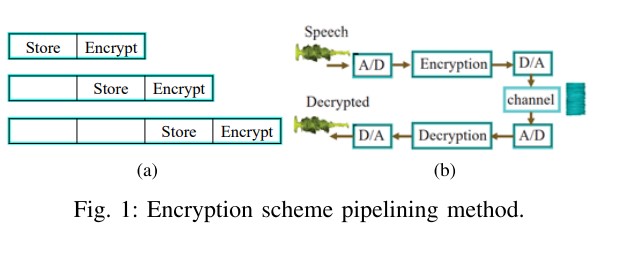

This paper introduces an FPGA design methodology of a sample and bit permutation speech encryption system. Pipelining method is used to build the proposed system, which can have different number of permutation levels. The security of the system is evaluated using entropy, Mean Squared Error (MSE) and correlation coefficients comparing the different permutation levels. The results demonstrate the security of the proposed system, which enables its utilization in speech telecommunication. Hardware resources comparison validates the efficiency of the system. The designs are simulated using Xilinx ISE 14.7 and realized on FPGA Xilinx Kintex 7. © 2018 IEEE.