Memristor FPGA IP core implementation for analog and digital applications

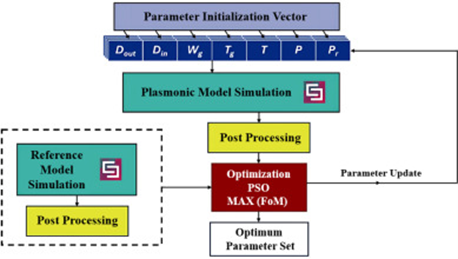

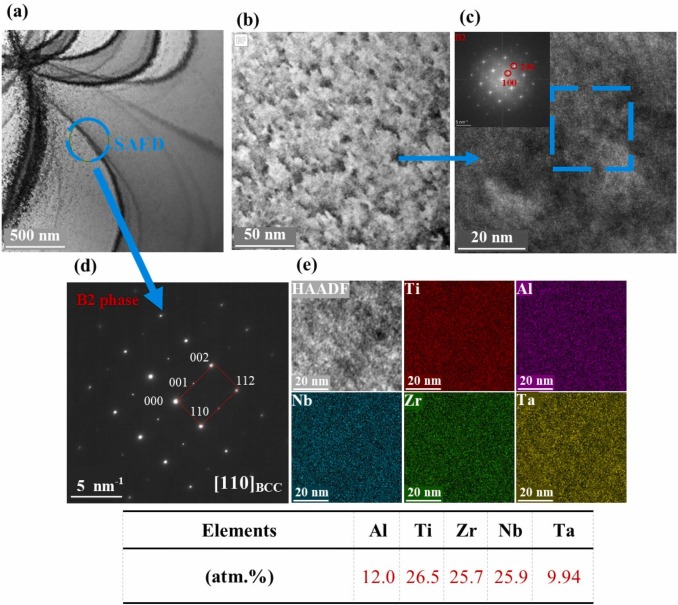

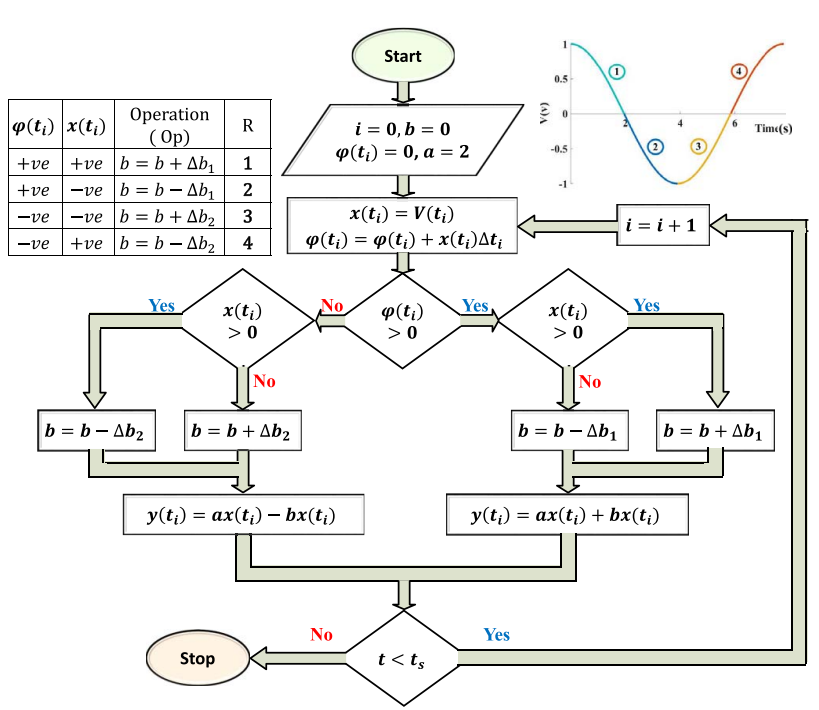

Exploring the nonlinear dynamics of the memristors is essential to be adequately used in the applications. Realizing memristor on FPGAs as an intellectual property (IP) core offers a flexible platform to realize different models. In the literature, few implementations have been proposed for simple and limited memristor model. In this brief, two discrete and continuous versatile memristor models alongside their FPGA realizations are proposed. These models can generate different pinched hysteric behaviors, such as symmetric, asymmetric pinched hysteresis, and multi-state switching behavior. In addition, the closed form expression for the enclosed area is derived to prove the memristive behavior. The proposed implementations have been successfully synthesized and verified on a Xilinx Nexys4 FPGA with less than 1% utilization and running up to 231 MHz. In order to test the functionality of the proposed cores, a digital implementation for the memrisitive-Chua chaotic circuit is implemented and verified experimentally. The experimental results show a good performance compared with MATLAB simulations and previous works. © 2018 IEEE.