Hardware Optimized FPGA Implementations of High-Speed True Random Bit Generators Based on Switching-Type Chaotic Oscillators

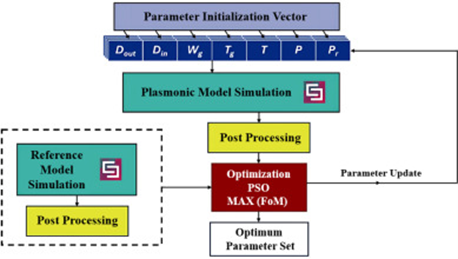

One of the important applications of chaotic oscillators is their employment as sources of entropy for True Random Bit Generators (TRBGs). In this work, we introduce high-speed TRBGs realized on a modular Field Programmable Gate Array (FPGA) hardware platform using two different switching-type chaotic oscillators. While both oscillators are autonomous, one is 3-D and the other is 4-D. This enables us to investigate and compare the advantages/disadvantages of higher dimensional chaotic oscillators on the throughput, hardware requirements and security of the generated bit-streams. For that purpose, two different implementations are described for each TRBG; a throughput-optimized architecture and a resource-optimized architecture that utilizes fewer FPGA blocks. In both cases, high speed is achieved by concatenating all state-space variables of each chaos generator into one variable. Furthermore, a new postprocessing method that enables the generated bit-streams to pass all NIST 800.22 statistical tests is introduced. Experimental results show that the throughput-optimized TRBG architecture, based on the 4-D system, can exceed 1882 Mbit/s. However, the resource-optimized TRBG architecture, based on the 3-D system, is the best in terms of FPGA resources and overall Figure of Merit. © 2018, Springer Science+Business Media, LLC, part of Springer Nature.