Gain-band self-clocked comparator for DC-DC converters hysteretic control

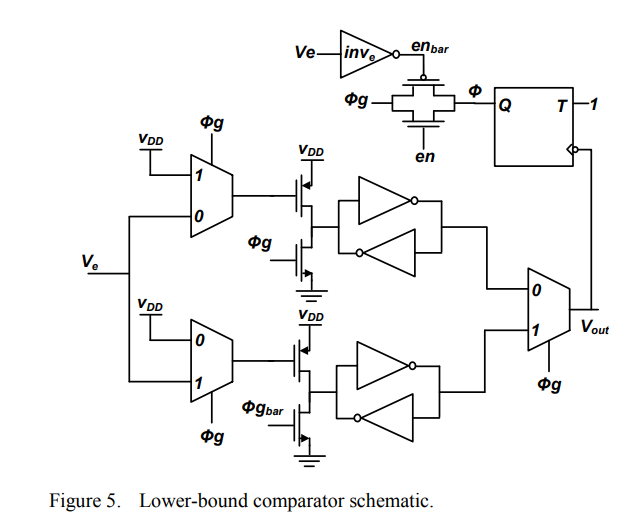

A novel digital comparator topology is presented. The proposed digital comparator cell uses transistors' ratio to program a fixed comparison level. A double-bound hysteretic control comparator, for DC-DC converters, is built using the proposed digital comparator cell. The hysteretic-band width variation, due to process effects, decreases with increased preamplifier stage gain and constitutes a fixed ratio of the hysteretic-band width. The proposed comparator does not require offset cancellation circuits, which reduces power consumption as well as the die area and increases the comparison speed. In addition, one preamplifier and one reference generation circuit are needed to build the double-bound comparison levels. The proposed topology also does not require a sampling clock. A prototype hysteretic control comparator is implemented in 65-nm TSMC low-power CMOS process. The hysteretic-band width exhibits a maximum variation of 300 μV for a 10 mV width. The comparator dissipates 80 μA of ground current to sample a 1.5 GHz input signal. ©2010 IEEE.