Accurate timing analysis of combinational logic cells engine using adaptive technique based on current source model

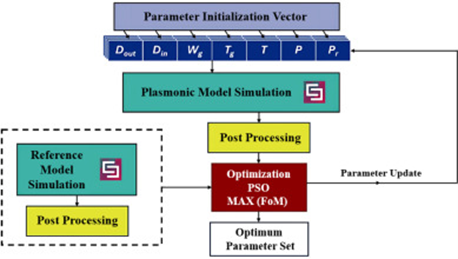

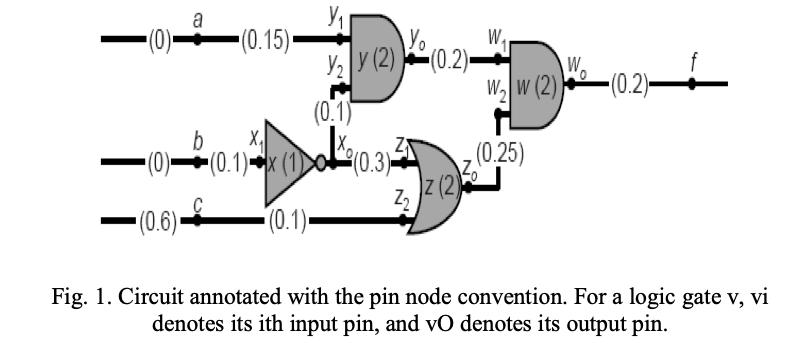

As the usage of very large scale integration (VLSI) in computers continues to increase, debugging of timing problems on actual hardware becomes more and more difficult. The post-layout gate-level simulation constitutes a critical design step for timing closure. The major drawback of traditional post-layout gate-level simulation is its long analysis time, which increases as design complexity increases. An alternative method is static timing analysis (STA), which can reduce analysis time. Going deeper through the nanometer technology, new STA techniques have to be present to provide more accurate results for cell delay models characterization. New STA techniques now go for current source based models (CSM) which are based on modeling MOSFETs as trans-conductance. In this paper, a SW engine is presented and used to perform a comparison on accuracy and speed between the default STA technique based on library lookup tables (LUT) and a proposed CSM-based technique for combinational logic cells. Moreover, an adaptive technique, which is based on utilizing both the LUT and CSM methods, is presented. The adaptive technique uses the method with the more accurate delay results when solving for circuits combined of NAND2X0, NOR2X0 and INVX0 standard cells. Also, provides the calculation for some metrics like (arrival time and slack delay values at each node in the combinational circuit). © 2013 IEEE.