A 12Gbps all digital low power SerDes transceiver for on-chip networking

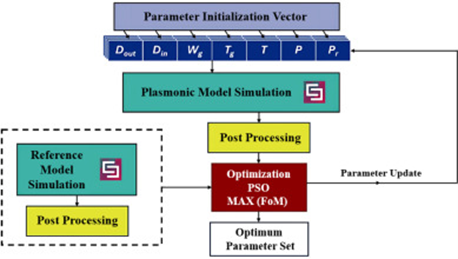

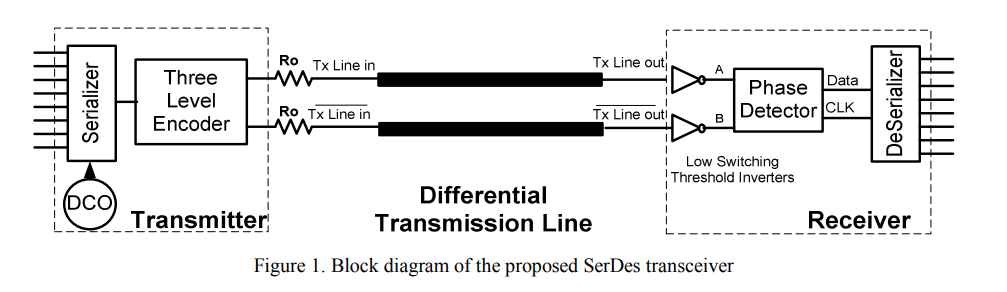

In this paper, a new self-timed signaling technique for reliable low-power on-chip SerDes (Serialization and DeSerialization) links is presented. The transmitter serializes 8 parallel bits at 1.5GHz, and multiplexes the 12Gbps serial data stream with a 24GHz clock on a single line using three level signaling. This new signaling technique enables the receiver to recover the clock from the data with a simple phase detector circuitry. Moreover, this technique is insensitive to jitter accumulated during signal propagation or at the receiver input because the clock signal is extracted from the multiplexed data stream. Hence, timing errors in the received signal reflects in both the data and the extracted clock, and the data will be sampled correctly. The SerDes transceiver was implemented for a 3mm long lossy on-chip differential transmission line in 65nm TSMC CMOS technology. A primary advantage of building an all digital SerDes transceiver is the ease of scaling with technology, and the power and area reduction. The total power consumed in the Tx/Rx pair with the transmission line is 15.5mWatt, which is very small as compared to similar published signaling architectures. © 2011 IEEE.