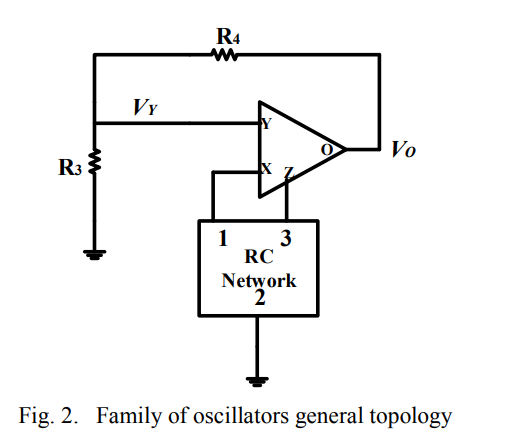

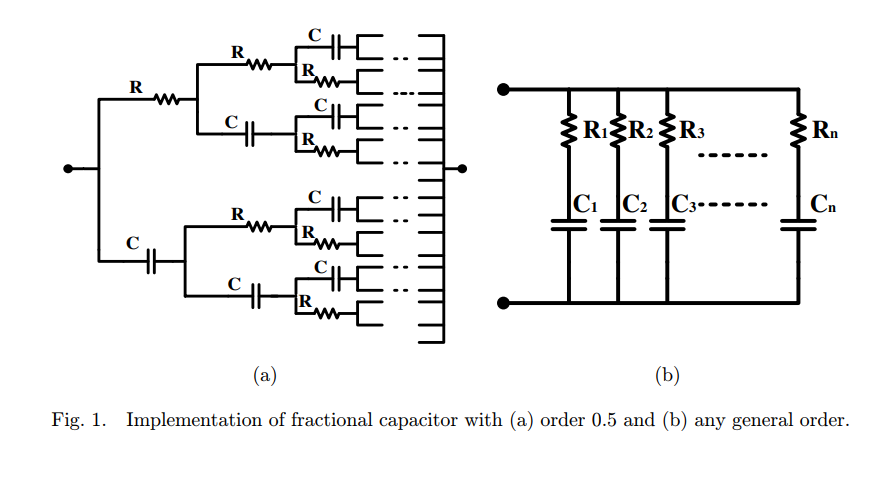

This paper presents a generalized family of fractional-order oscillators based on single CFOA and RC network. Five RC networks are investigated with their general state matrix, and design equations. The general oscillation frequency, condition and the phase difference between the oscillatory outputs are introduced in terms of the fractional order parameters. They add extra degrees of freedom which in turn increase the design flexibility and controllability that is proved numerically. Spice simulations are introduced to validate the theoretical findings. © 2017 IEEE.

This paper presents a generalization of six well-known quadrature third-order oscillators into the fractional-order domain. The generalization process involves replacement of three integer-order capacitors with fractional-order ones. The employment of fractional-order capacitors allows a complete tunability of oscillator frequency and phase. The presented oscillators are implemented with three active building blocks which are op-Amp, current feedback operational amplifier (CFOA) and second generation current conveyor (CCII). The general state matrix, oscillation frequency and condition are

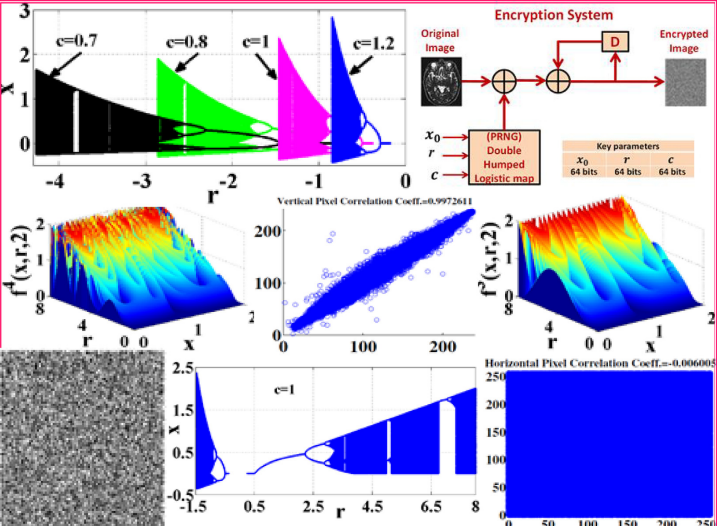

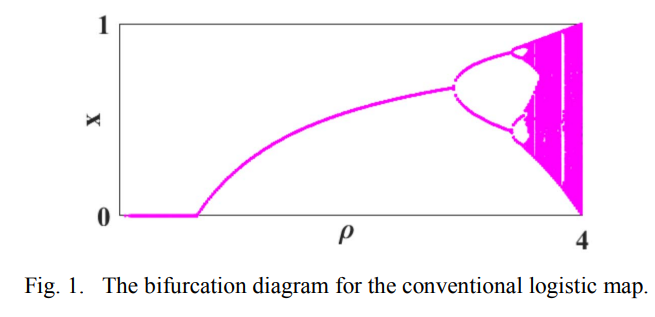

This paper presents the design of the generalized Double Humped (DH) logistic map, used for pseudo-random number key generation (PRNG). The generalized parameter added to the map provides more control on the map chaotic range. A new special map with a zooming effect of the bifurcation diagram is obtained by manipulating the generalization parameter value. The dynamic behavior of the generalized map is analyzed, including the study of the fixed points and stability ranges, Lyapunov exponent, and the complete bifurcation diagram. The option of designing any specific map is made possible through

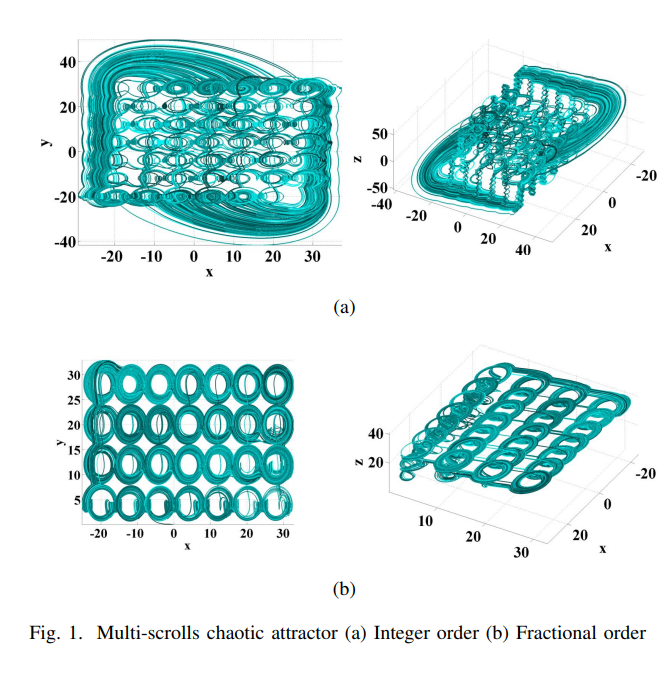

Exploring the implementation of fractional calculus is essential to be adequately used in several applications. This paper introduces an FPGA design methodology of fractional order multi-scrolls chaotic system. Hardware resources comparison proves the efficiency of the proposed method. The designs are simulated using Xilinx ISE 14.7 and realized on FPGA Xilinx Artix 7. Different interesting attractors are realized under various parametric changes with distinct step sizes for different fractional-orders. To verify the proposed fractional order multi-scrolls chaotic system on FPGA, experimental

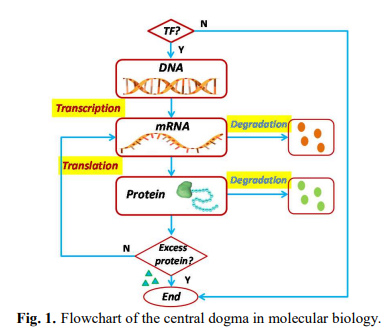

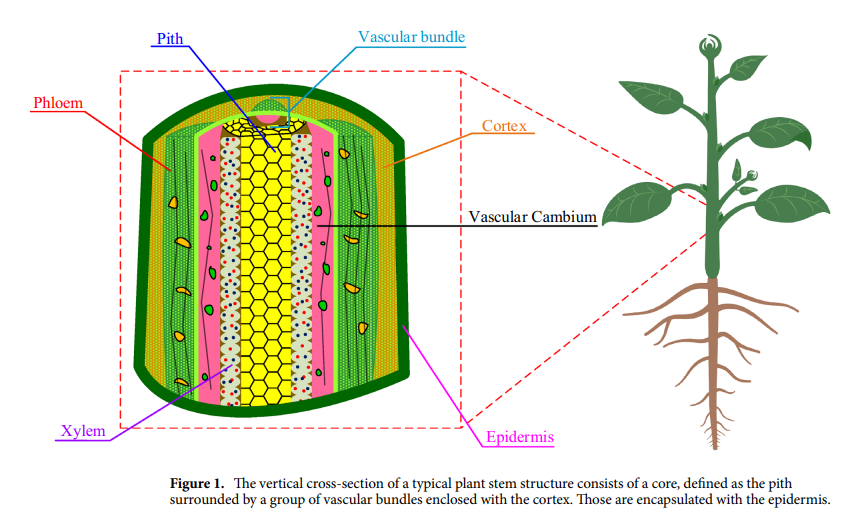

This paper presents a practical emulator of a generalised fractional-order model for gene regulation process, in an analog platform. The presented emulator is based on the second-generation current conveyor (CCII) and implemented using AD844 chips. The emulator realises a proposed generalised mathematical model for gene expression. The model sums up three different single models; the constitutive gene model, the induced gene expression under the effect of activators and repressors models. The generalised model is based on fractional-order differential equations where the concentration of the

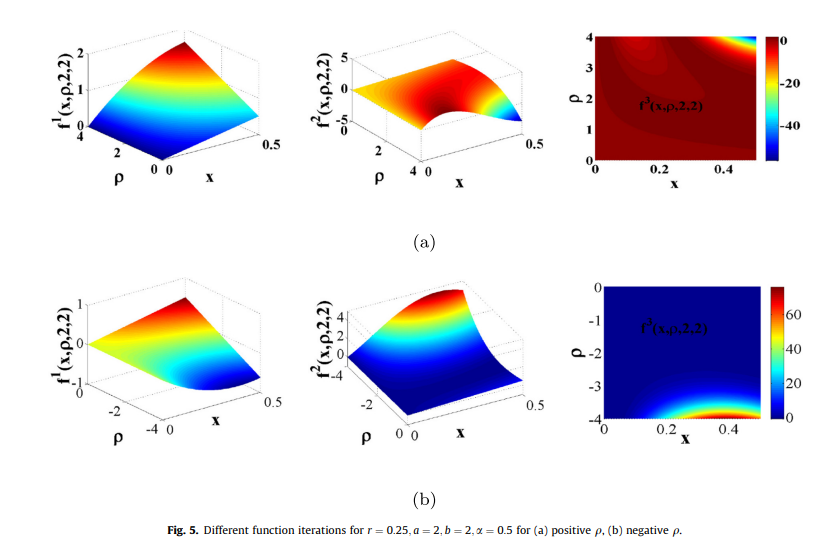

This paper introduces the design of a generalized fractional order logistic map suitable for pseudorandom number key generators and its application in an encryption system based on FPGA. The map is generalized through two parameters (a,b) where complete analysis of their effect on the map is detailed, which gives more control on the map chaotic regions. The vertical map and the zooming map presented in this paper are two special maps extracted from the generalized map with their detailed analysis. Not only the positive bifurcation, but also the negative side is discussed through this paper

This paper presents the dynamic analysis of two discrete logistic chaotic maps versus the conventional map. The first map is the fractional logistic map with the extra degrees of freedom provided by the added number of variables. It has two more variables over the conventional one. The second map is the double-humped logistic map. It is a fourth-order map which increases the non-linearity over the conventional one. The dynamics of the three maps are discussed in details, including mathematical derivations of fixed points, stability analysis, bifurcation diagrams and the study of their chaotic

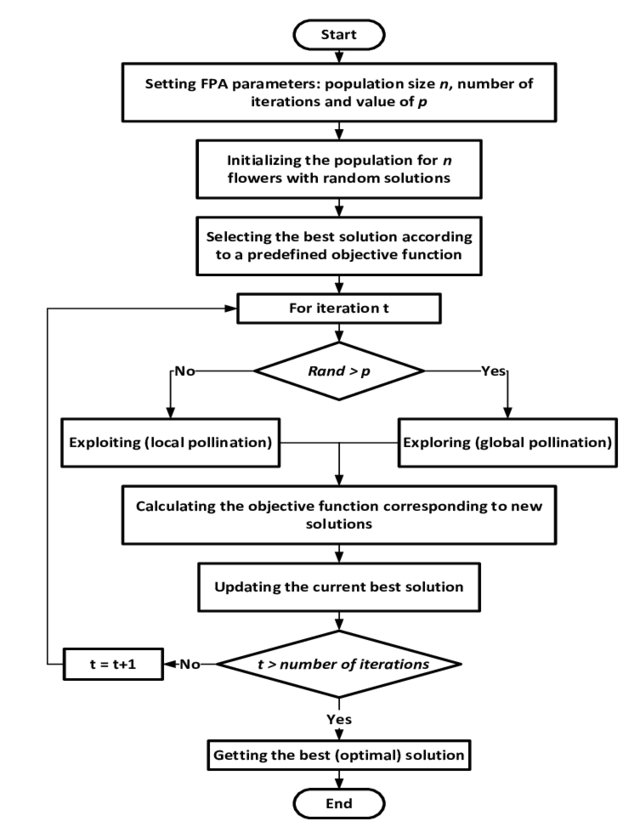

Power management and saving in energy harvesting-based biomedical wearable devices are mandatory to ensure prolonged and stable operation under a stringent power budget. Thus, power-aware task scheduling can play a key role in minimizing energy consumption to improve system durability while maintaining device functionality. This paper proposes a novel biosensor task scheduling for optimizing energy consumption through wearable biomedical devices. The proposed approach is based on Flower Pollination Algorithm (FPA). The biomedical functionality constraints are enforced with a Hamming-based

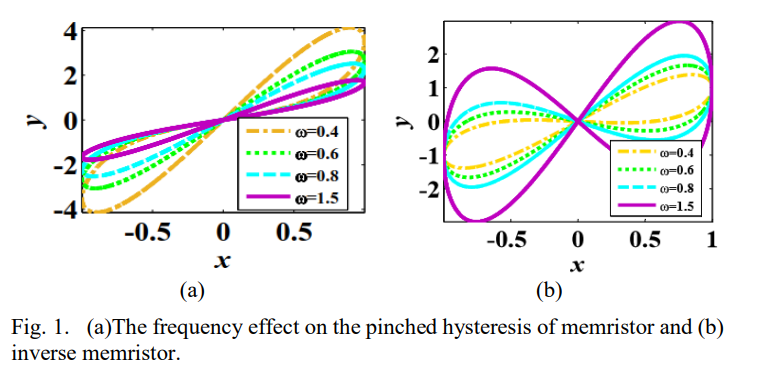

The paper aims to propose three different inverse memristor emulators based on serveral active blocks. One of the presented emulator realizes employing second generation current conveyor (CCII) andcanalog voltage multiplier with passive elements. The other two introduced emulators are designed using cureent feedback operational amplifier (CFOA) with two switches or two BJT transistor. One of the proposed emulators has the advantages that it switches between the inverse and memristor at the same time but in different frequency with less number of components. The introduced circuitry are