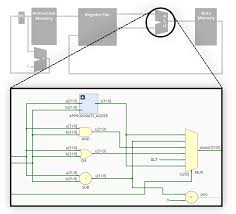

Single-Cycle MIPS Processor based on Configurable Approximate Adder

Enhancing computer architecture performance is a significant concern for architecture designers and users. This paper presents a novel approach to computer architecture design by using an approximate adder with configurable accuracy in a single-cycle MIPS processor as a study case. Using approximate adders decreased the delay on the expense of the design area. Using approximate computing with the MIPS processor, the timing performance has been improved by 253.4% compared to the lookahead adder. It has been implemented and tested using System-Verilog. © 2022 IEEE.