A novel approach for SVA generation of DDR memory protocols based on TDML

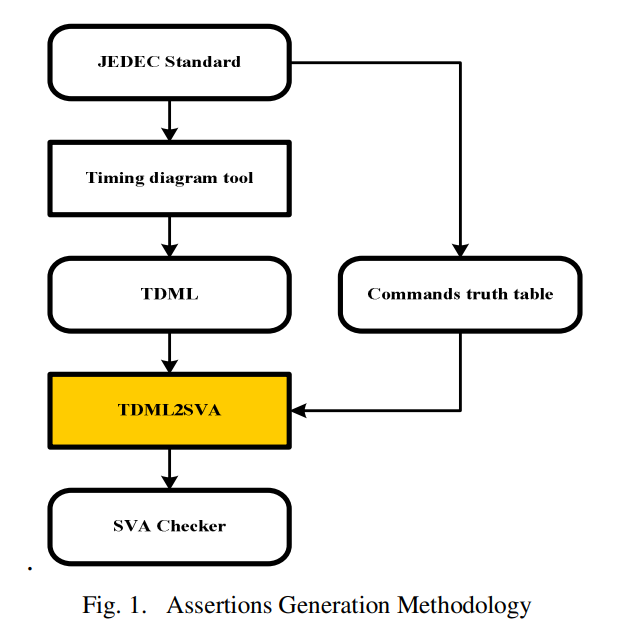

System Verilog Assertions (SVA) is widely used by hardware designers and verification engineers to apply Assertion Based Verification (ABV) methodology on their hardware designs. However, the ambiguity of design specifications specified by different protocol standards in general and JEDEC memory protocol standards in specific imposes numerous difficulties on designers and verification engineers when translating design specifications into SVA. This motivated us to find a simple way to capture design specifications from JEDEC standard and automatically generate SVA that can be used as checkers for DDR memory protocols. In this paper, we propose a new method to capture design specifications using a timing diagram tool that documents the captured design specifications in a Timing Diagram Mark up Language (TDML) based format and generate SVA from the TDML document. The viability and the potential of our work are demonstrated with an Industrial case study using JEDEC LPDDR3 Memory Protocol Standard. © 2015 IEEE.