Maximizing USRP N210 SDR transfer rate by offloading modulation to the on-board FPGA

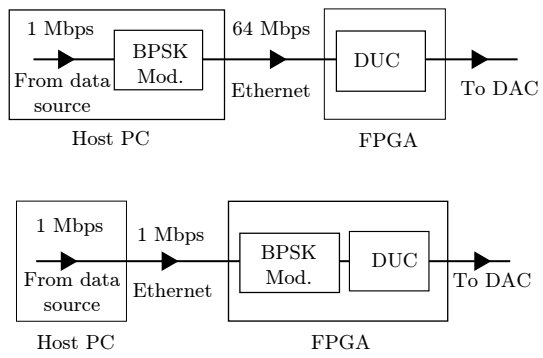

One of the challenges of the design of Software Defined Radios (SDR) is to maintain a high level of reconfigurability without sacrificing data rates. In this paper, we consider the USRP N210, which is an SDR kit made by Ettus Research. It consists of an FPGA connected to an RF front-end. The USRP is operated by a host computer where most of the processing is done while the FPGA is used mainly to control the RF front-end, manage communication with the host, and convert sample rates. The maximal rate supported by the USRP hardware can not be practically achieved due to the bottleneck in the data transfer between the host and USRP and the limited computational ability of the computer. To deal with this problem, we implement a modulator and demodulator in the FPGA of the USRP. The proposed system is capable of processing data at the maximum sample rate supported by the hardware. This is accomplished by transferring only raw data between host and USRP, reducing transfer rate by up to 64 times; thus, bypassing the host transfer bottleneck. Additionally, offloading some of the processing to the FPGA makes communication at the maximum rate achievable with an off the shelf computer. An evaluation of the performance of the suggested system from the communication perspective is performed. We also showcase the system's ability to work at the maximum sample rate supported by the USRP. © 2016 IEEE.