Image

Efficient Implementation of Reconfigurable Machine Learning IP Cores on FPGA

Research Project

This project's aim is to develop a working flow providing a better and an efficient way for implementing Machine Learning algorithms having a balance between high performance and low power consumption.

Objective/Contributions:

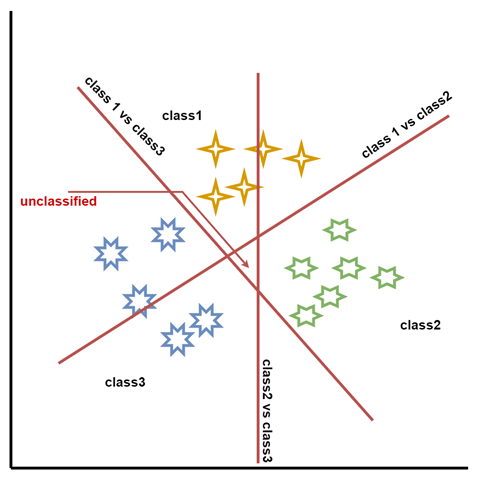

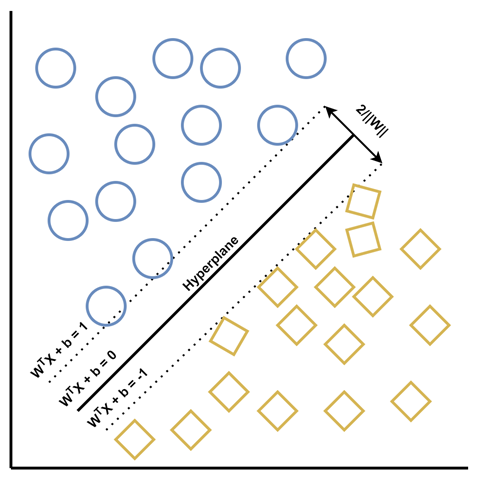

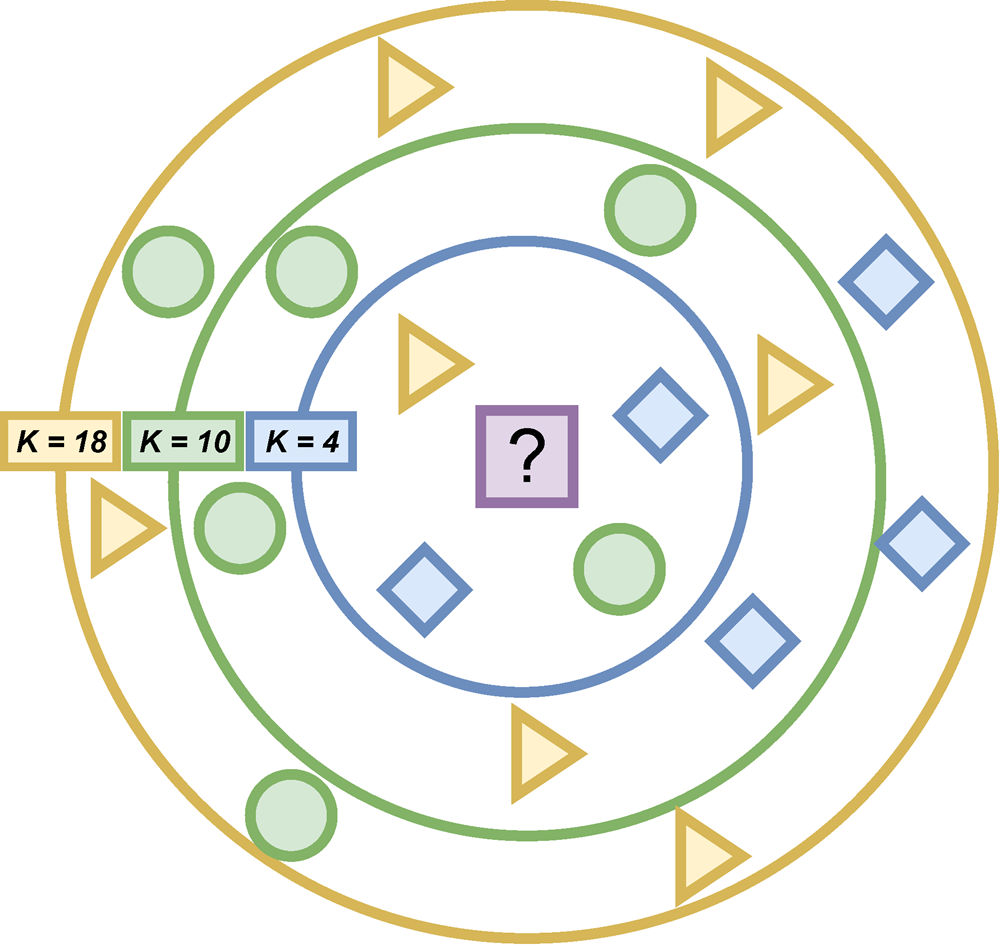

- Software Implementation of Machine Learning Algorithms

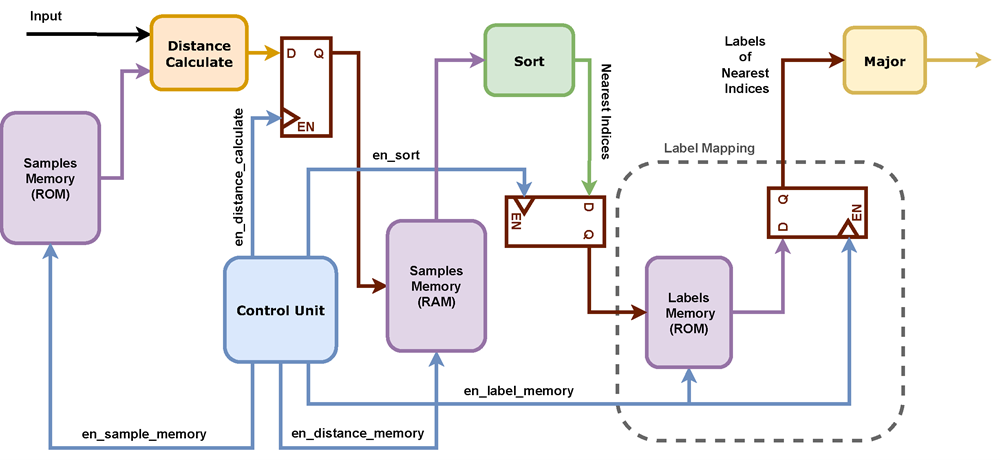

- Hardware Implementation of Machine Learning Algorithms

- Efficient Power Consumption

- Reconfigurable Design of ML FPGA IP Cores

Outcome Publications:

Mohammed H. Yacoub, Samar M. Ismail, Lobna A. Said, Ahmed H. Madian, Ahmed G. Radwan, "Generic Hardware Realization of K Nearest Neighbors on FPGA", The 34th International Conference on Microelectronics (ICM), Morroco, December 2022