In this study, we show that the discharge voltage pattern of a supercapacitor exhibiting fractional-order behavior from the same initial steady-state voltage into a constant resistor is dependent on the past charging voltage profile. The charging voltage was designed to follow a power-law function, i.e. [Formula: see text], in which [Formula: see text] (charging time duration between zero voltage to the terminal voltage [Formula: see text]) and p ([Formula: see text]) act as two variable parameters. We used this history-dependence of the dynamic behavior of the device to uniquely retrieve

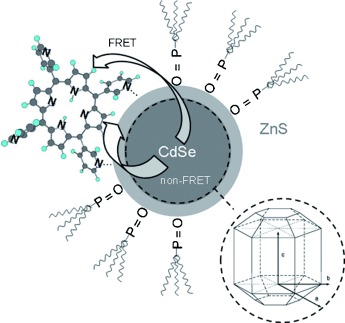

Functional dye molecules, such as porphyrins, attached to CdSe quantum dots (QDs) through anchoring meso-pyridyl substituents, form quasi-stable nanoassemblies. This fact results in photoluminescence (PL) quenching of the QDs both due to Förster resonance energy transfer (FRET) and the formation of non-radiative surface states under conditions of quantum confinement (non-FRET). The formation process is in competition with the ligand dynamics. At least two timescales are found for the formation of the assemblies: 1) one faster than 60 s attributed to saturation of empty attachment sites and 2)

Well-defined ultra-thin ‘wire’ like cadmium sulfide (CdS) nanostructures have been synthesized by applying simple cost-effective hydrothermal route. The content of nanostructures modifies the nature of surface interaction between two liquid crystal (LC) components as revealed by optical and electrical investigation. Those synthesized nanowires have an average diameter of about 7–10 nm and length up to several micrometers region. A possible mechanism has been proposed and the addition of cataionic surfactant cetyltrimethylammonium bromide (CTAB) into the two mixed-solvents would play an

This paper proposes a generalized topology of a fractional-order inverse filter (FOF) using operational transresistance amplifiers (OTRA) block. Seven different configurations are extracted from the introduced topology employing generalized admittances. The generalized admittances increase the flexibility to provide different types of FOFs such as inverse fractional high pass filter (FHPF), inverse fractional low pass filter (FLPF), inverse fractional bandpass filter (FBPF), and inverse fractional notch filter (FNF). Numerical and PSPICE simulation results are presented for selected cases to

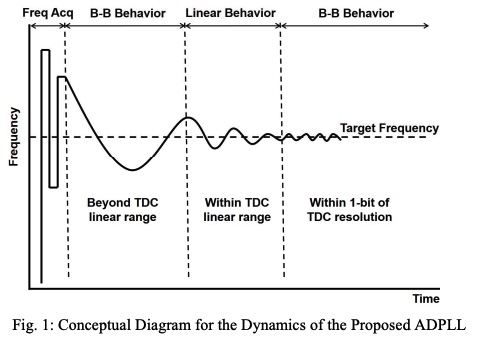

A hybrid Time to Digital Converter (TDC) - Bang Bang (BB) All Digital Phase Locked Loop (ADPLL) architecture is proposed to optimize power, area, lock time, and design complexity. The Hybrid ADPLL architecture utilizes a low resolution two synthesizable Time to Digital Converters to achieve fast lock time, and then switches to a Bang-Bang like architecture once it is in the locked state. Such hybrid architecture enables the ADPLL to achieve lock time in less than 1 μ sec using an adaptive proportional derivative digital loop filter while consuming a power of 5.1 mW when locked at 4GHz with 1

In this paper, a fast control scheme is presented for the problem of Q-S synchronization between fractional chaotic systems with different dimensions and orders. Using robust control law and Laplace transform, a synchronization approach is designed to achieve Q-S synchronization between n-D and m-D fractional-order chaotic systems in arbitrary dimension d. This paper provides further contribution to the topic of Q-S synchronization between fractional-order systems with different dimensions and introduces a general control scheme that can be applied to wide classes of fractional chaotic and

Ternary number system offers higher information processing within the same number of digits when compared to binary systems. Such advantage motivated the development of ternary processing units especially with CNTFET which offers better power and delay results compared to CMOS-based realization. In this paper, we propose a variety of circuit realizations for the ternary memory elements that are needed in any processor including ternary D-latch, and ternary D-flip-flop. These basic building blocks are then used to design a ternary register file with multiple read and write ports. This paper is

Modularity concepts attracted the attention of many researchers as it plays an important role in product design problems. Modularity requires dividing a product into a set of modules that are independent between each other and dependent within. The product is represented using Design Structure Matrix (DSM). DSM works as a system representation tool; it visualizes the interrelationship between product elements. In this research, a comparison is conducted between four optimization algorithms: Emperor Penguins Colony (EPC), First Modified Emperor Penguins Colony (MEPC1), Second Modified Emperor

This paper proposes a new fractional-order multi-scrolls chaotic system. More complex systems and flexible ranges of the chaotic behavior are obtained due to the extra parameters added by the fractional-order. The proposed system has novel complex chaotic behaviors. The effect of changing the system parameters on the system behavior is investigated and their bifurcation diagrams have been provided. The MLE for the proposed system in integer and fractional domain has been discussed. It shows that the proposed chaotic system is richer in the case of fractional-order. A novel FPGA design

In this paper, a new type of chaos synchronisation between different dimensional chaotic systems is proposed. The novel scheme is called F-M synchronisation, since it combines the inverse generalised synchronisation with the matrix projective synchronisation. In particular, the proposed approach enables F-M synchronisation to be achieved between n-dimensional master system and m-dimensional slave system in different dimensions. The technique, which exploits nonlinear controllers, stability property of integer-order linear continuous-time dynamical systems and Lyapunov stability theory, proves