Memristor-based quinary half adder

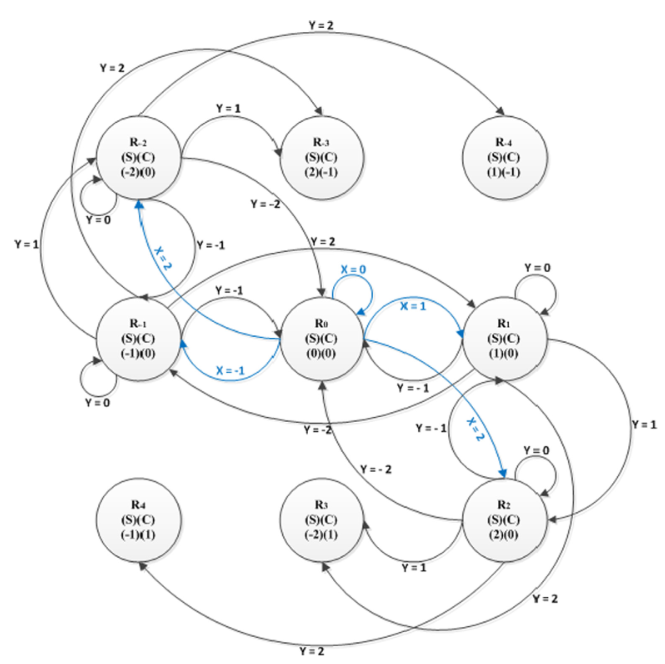

This paper theorizes the possibilities of generalizing a memristor based ternary adder circuit, to a memristor based multi-valued logic adder. The proposition tries to achieve the theoretical advantages of processing different numbering systems, increasing the density, and decreasing the processing time, by utilizing the memristor properties and dynamics. This is done using a memristor cell based circuit structure. The memristor is quantized to more levels in order to accommodate more values of logic being processed. Quinary numbering system is used to demonstrate the generalization, then a process of generalization is shown. Circuit modifications can be made to process different numbering systems. © 2018 Elsevier GmbH