FPGA realization of a speech encryption system based on a generalized modified chaotic transition map and bit permutation

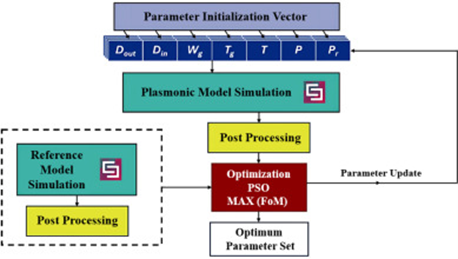

This paper proposes a generalized modified chaotic transition map with three independent parameters. A hardware speech encryption scheme utilizing this map along with a bit permutation network is presented. While the transition map’s generalization introduces additional parameters, the modification enhances its chaotic properties and overcomes the finite range of the control parameter and dynamical degradation problems. The modification also presents a simplification for the hardware realization of the exponentiation operation in the map’s equation because the modified output range allows conversion from the linear domain to the Logarithmic Number System (LNS). Mathematical analysis of the map is presented, where exact nonlinear expressions of the dependent parameters are derived and validated through simulations. To further simplify the hardware realization, the complicated nonlinear expressions are linearized and the introduced approximation error is quite acceptable. The encryption scheme is simulated using Xilinx ISE 14.7 and realized on Xilinx Nexys 4 Artix-7 FPGA with a throughput of 1.526 Gbit/sec. The security and efficiency of the hardware speech encryption scheme are validated and the performance is compared with recent works that provided experimental results on Pseudo-Random Number Generation (PRNG) and speech encryption. © 2018, Springer Science+Business Media, LLC, part of Springer Nature.