Breadcrumb

Circuit Theory and Applications

Statistical Investigation of Scientific Journals Impact Factors in Relation to Benford's Law

Benford's law (BL) has been used as a tool for the detection of possible data manipulation in datasets. The statistics of the first digit(s) of the observed values are compared to a set of expected values given by BL, and violations signal possible data anomalies. Though this method is first used for economical purposes, it has been recently used in bibliometric statistical analyses. The method provides alert that records may have certain unusual trends. In the present work, we investigate the impact factor statistics for 24 years starting from 1997 up to 2021, for open access and subscribed

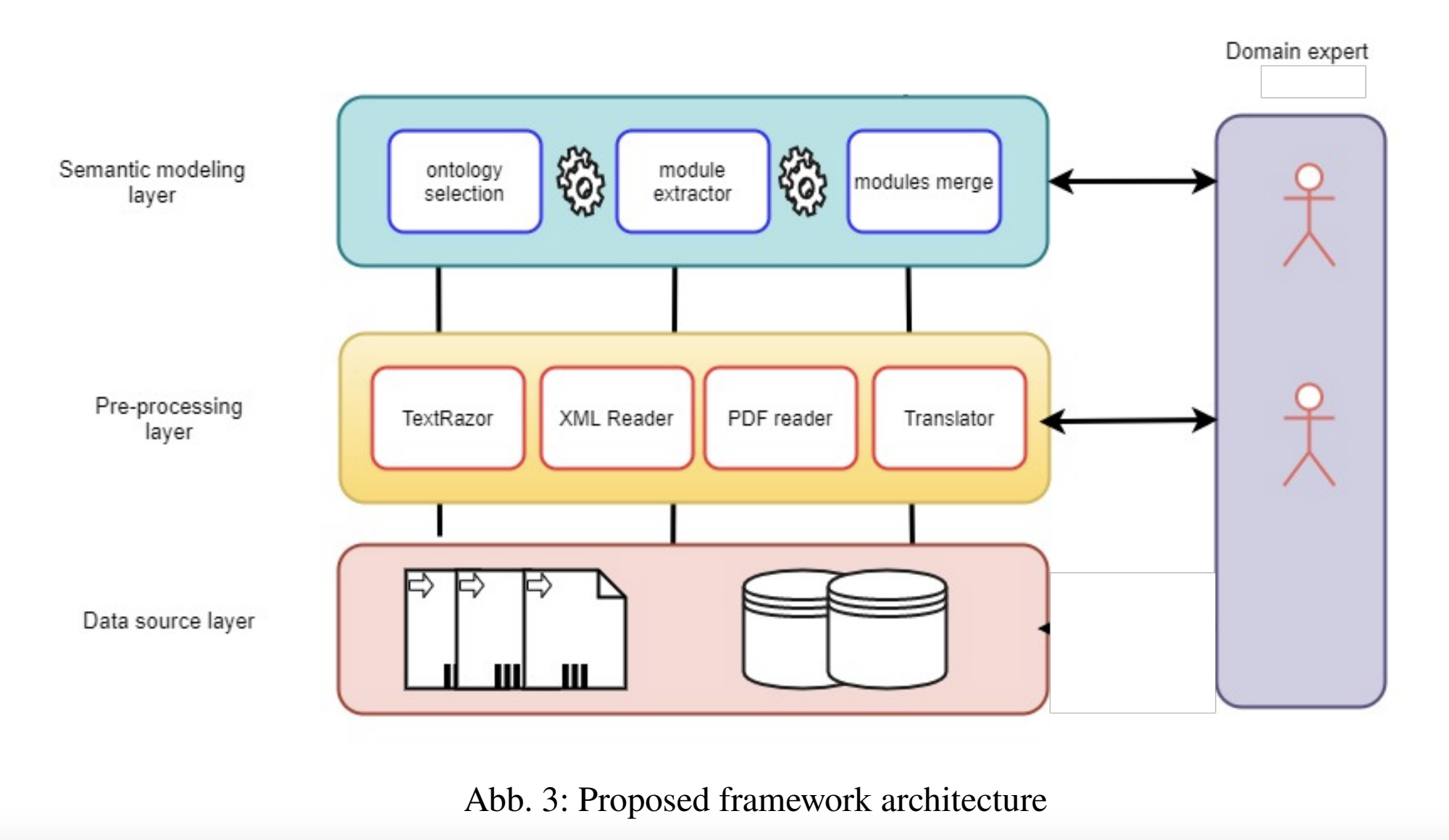

A Core Ontology to Support Agricultural Data Interoperability

The amount and variety of raw data generated in the agriculture sector from numerous sources, including soil sensors and local weather stations, are proliferating. However, these raw data in themselves are meaningless and isolated and, therefore, may offer little value to the farmer. Data usefulness is determined by its context and meaning and by how it is interoperable with data from other sources. Semantic web technology can provide context and meaning to data and its aggregation by providing standard data interchange formats and description languages. In this paper, we introduce the design

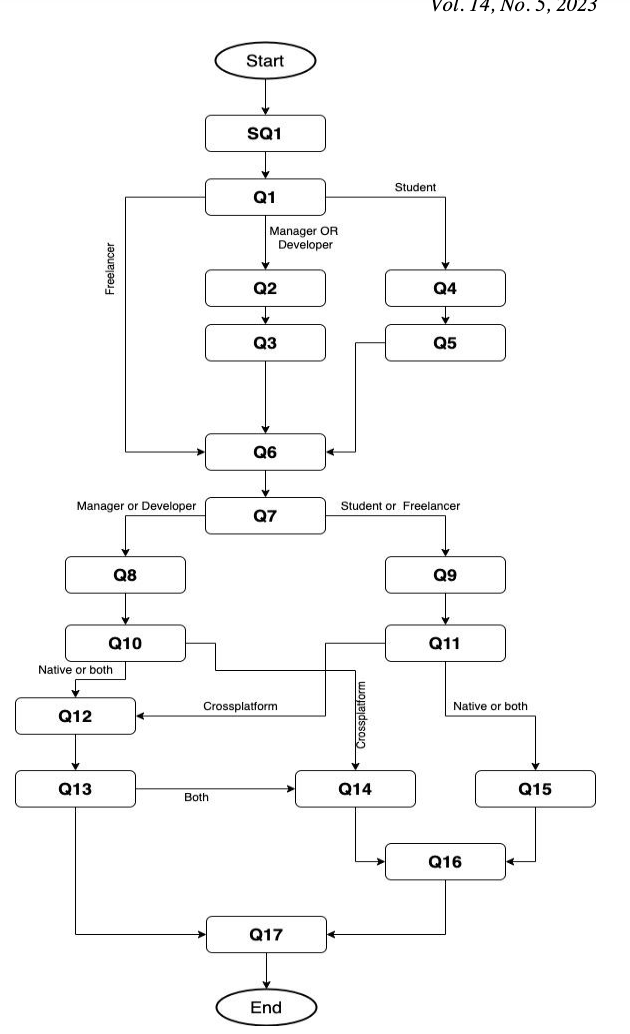

Industrial Practitioner Perspective of Mobile Applications Programming Languages and Systems

The growth of mobile application development industry made it crucial for researchers to study the industry practices of choosing mobile applications programming languages, systems, and tools. With the increased attention of cross-platform mobile applications development from both researchers and industry, this paper aims at answering the question of whether most of the industries are using cross-platform development or native development. The paper collects feedback about industry’s most used mobile development systems. In addition, it provides a map of the different technologies used by

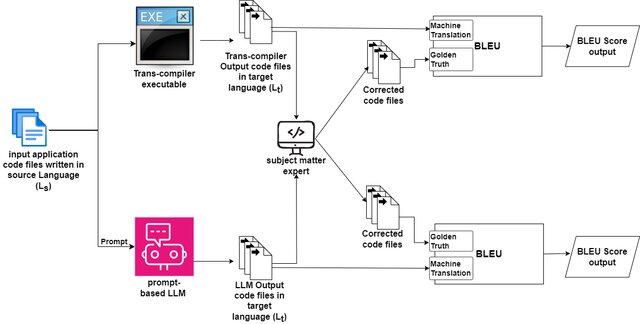

Compiler-based Web Services code conversion model for different languages of mobile application

Mobile applications are very popular nowadays. The two most common platforms depend on different languages to have native performance. Most trans-compiler-based converters between those languages didn't take webservices conversion into consideration. However, in recent years, mobile applications developers have used web services for lighter and more dynamic mobile applications. Therefore, it becomes crucial to include web services mapping to the trans-compiler-based code converters for mobile applications code. In this paper, we present a model for web service trans-compiler code mapper from

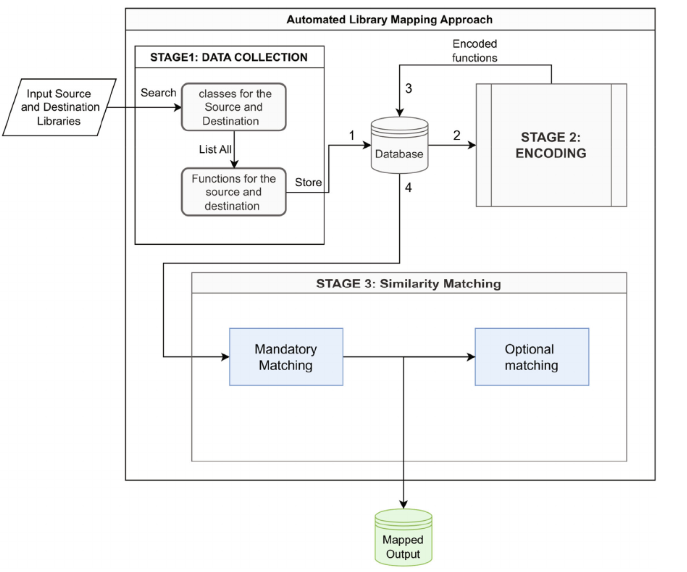

Automated library mapping approach based on cross-platform for mobile development programming languages

Context: The most popular mobile platforms, Android and iOS, are traditionally developed using native programming languages—Java and Kotlin for Android, and Objective-C followed by Swift for iOS, respectively. Due to their popularity, there is always a demand to convert applications written for one of these two platforms to another. Cross-platform mobile development is widely used as a solution where an application is written once and deployed on multiple platforms written in several other programming languages. One common cross-platform approach that has been used recently by some research

Mobile Application Code Generation Approaches: A Survey

With the extensive usage of mobile applications in daily life, it has become crucial for the companies of software to develop applications for the most popular platforms such as Android and iOS in the shortest possible time and at the lowest possible cost. However, ensuring consistent UIs and functionalities among cross-platform versions can be challenging and costly since different platforms have their own UI controls and programming languages. Also, when cross-platform tools are used, it is always time consuming to learn a new language. Many solutions were proposed to achieve the native

Trans-Compiler-Based Conversion from Cross-Platform Applications to Native Applications

Cross-platform mobile application development is emerging widely in the mobile applications industry. Cross-platform Frameworks (CPFs) like React Native, Flutter, and Xamarin are used by many developing companies. The technology these frameworks use faces performance and resource use efficiency limitations compared to native applications. The native applications are written in the native languages of the platforms. Trans-complier-based conversion between native languages of different platforms of mobile applications has been addressed in recent research. However, the problem statement needed

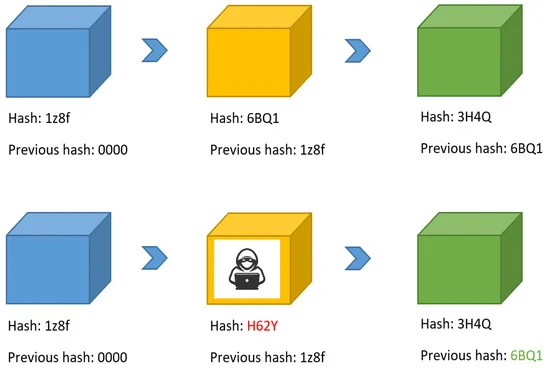

Smart Automotive Diagnostic and Performance Analysis Using Blockchain Technology

The automotive industry currently is seeking to increase remote connectivity to a vehicle, which creates a high demand to implement a secure way of connecting vehicles, as well as verifying and storing their data in a trusted way. Furthermore, much information must be leaked in order to correctly diagnose the vehicle and determine when or how to remotely update it. In this context, we propose a Blockchain-based, fully automated remote vehicle diagnosis system. The proposed system provides a secure and trusted way of storing and verifying vehicle data and analyzing their performance in

Semi-Supervised Machine Learning Applications in RAN Design: Towards Data-Driven Next Generation Cellular Networks

The explosive growth of mobile internet services and demand for data connectivity boosts the innovation and development in Radio Access Network (RAN) to define how next generation mobile networks will look like. Continuous improvement in existing RAN is crucial to meet very strict speed and latency requirements by different mobile applications with minimum investments. Exploiting the advancement in Machine Learning and AI-driven algorithms is essential to tackle these challenges in different functions within the RAN domain. In this paper we surveyed how to leverage different clustering

Design and Implementation of a Dockerized, Cross Platform, Multi-Purpose Cryptography as a Service Framework Featuring Scalability, Extendibility and Ease of Integration

Following cybersecurity st and ards nowadays is becoming one of the highest priorities to the digital specialists. Due to the global direction to apply digital transformation, data security is a concern. It becomes crucial to ensure data confidentiality, integrity, and availability whether while transmitting, at rest or even while processing it. The difficulty being faced by organizations, is the challenge of applying the needed security measures. Also, implementing, and maintaining the cryptographic algorithms that ensure the wellness of the data encryption. Having a crypto library or a